# THE USE OF SIMULATION IN SEMICONDUCTOR TECHNOLOGY DEVELOPMENT

D. C. Cole<sup>1</sup>, E. M. Buturla<sup>1</sup>, S. S. Furkay<sup>1</sup>, K. Varahramyan<sup>1</sup>, J. Slinkman<sup>1</sup>, J. A. Mandelman<sup>1</sup>, D. P. Foty<sup>1</sup>, O. Bula<sup>1</sup>, A. W. Strong<sup>1</sup>, J. W. Park<sup>1</sup>, T. D. Linton Jr<sup>1</sup>, J. B. Johnson<sup>1</sup>, M. V. Fischetti<sup>2</sup>, S. E. Laux<sup>2</sup>, P. E. Cottrell<sup>1</sup>, H. G. Lustig<sup>1</sup>, F. Pileggi<sup>1</sup> and D. Katcoff<sup>1</sup>

<sup>1</sup>IBM General Technology Division, Essex Junction, Vermont 05452, U.S.A. and <sup>2</sup>IBM Research Division, Thomas J. Watson Research Center, P.O. Box 218, Yorktown Heights, NY 10598, U.S.A.

(Received 28 November 1989; in revised form 5 February 1990)

Abstract—An overview is presented on the types of problems encountered in semiconductor technology development that are actively studied today via simulation methods. Most of the simulation examples presented here are ones that have been explicitly used in actual industrial semiconductor device design cycles to aid in the optimization of device structures. The examples described here include process simulations, such as the diffusion of dopant atoms, oxidation, etching, deposition, and epitaxial growth, as well as device simulations, which predict the flow of charge carriers and field distribution within a semiconductor device, given its material structure and operating conditions. The main aim here is to illustrate, by example, some of the capabilities of state-of-the-art simulators used in characterizing and predicting semiconductor process and device-related phenomena. We will attempt to outline the degree of sophistication of the physics incorporated in such simulation programs, and provide some contrast to the fundamental physics required for a complete physical description. As will be indicated, simulation development necessarily involves molding the appropriate physical models and numerical algorithms into a package that can be handled in a reasonable length of time by modern computing systems. We briefly outline some of the advances that have been made, and some concerns that remain, in such simulation development.

#### 1. INTRODUCTION

In this article, we will present a number of pictorial examples that demonstrate various uses of simulation in semiconductor technology development. By means of these examples, we will survey various capabilities of simulators we have ourselves used on a regular basis to aid in the development of advanced semiconductor devices. Our belief is that such examples will quickly portray to the reader of this special issue of *Solid-State Electronics* how the applied physical theory often discussed here has been used for simulation experiments within industry, as well as academia.

To accomplish this task, yet limit the overview to a reasonable length, we will need to de-emphasize the details of any one physical model, as well as the numerical solution techniques involved in the simulation, and simply refer the reader to the appropriate literature on that subject. Our intent is to give the reader a strong feel for the wide range of problems that can be solved with today's simulators. This work is meant to complement the expected detailed discussion on physical models in the remainder of this issue, which, due to the complicated physical behavior involved, generally needs to be embodied in a simulation program to extract quantitative predictive results.

The simulation examples we will discuss here involve predictions of *process* behavior related to the

fabrication of semiconductor devices, such as the diffusion of dopant atoms in crystalline materials, oxidation, ion implantation, etching, and deposition of thin films. Given the structure of a semiconductor device via such process simulation, the resulting device behavior can then be simulated by calculating the transport of carriers and associated field distributions due to applied, external fields. For both of these cases, we will examine real problems that have been studied at IBM during the course of semiconductor technology device development over the past 15 years. Our author list reflects our intention to gather a number of simulation examples that have been used as active research tools and aids for characterizing and predicting process and device behavior of semiconductor products under development.

To begin, we note that there are already a number of review papers related to process and device simulation[1–13], as well as books[14–21], and numerous articles dealing with specific models and applications involving semiconductor-related simulation programs. The field is still evolving, as more detailed physics is incorporated into such programs, as more powerful numerical algorithms are investigated, and as the capabilities of computing systems continue to improve. Our paper will present, by example, what we believe to be a fairly up-to-date snapshot in time of this evolving field of semiconductor-simulation capability.

However, we note here that our examples are almost exclusively drawn from simulation programs developed within IBM, such as FEDSS[22-24], TRIM[25,26], FIELDAY[27-39], OYSTER[40-42], and DAMOCLES[43-46], with an example on lithography taken from the University of California at Berkeley program, SAMPLE[47-52]. Our "survey" then should not be regarded as a review on the details of simulators in existence today, but rather as an overview on the types of problems such simulators are capable of handling, using IBM simulators for illustration.

Nevertheless, the reader should be aware that a number of other comprehensive simulation programs are in existence today. Indeed, several universities have created programs and released them for public use, such as the device programs PISCES[53], SEDAN[54], HFIELDS[55-57], and MINIMOS [58-61], and the process programs SUPREM [[62], II[63], III[64] and IV[65-67]. Also, other development groups in academia and industry have developed their own set of simulation programs. Here we mention, as a partial list, the programs PREDICT[68,69], IMPACT[70], SMART-P[71], and COMPOSITE[72], as well as the set of programs by AT&T and TMA[73]. Each of these programs has certain advantages over one another regarding specific physical models, the precise mathematical equations solved, the numerical algorithms used, and the pre- and post-processing handling of data. (For specific comparisons between simulation programs, see such yearly conference proceedings as NASECODE and NUPAD, which often contain papers that emphasize the dissemination of this type of information.)

The outline of the remainder of our paper consists, first of all, of a brief background in Section 2 on modeling activities in semiconductor technologies. Here, we will contrast various approaches that have been used for simulation-related studies, and attempt to convey what we mean by modeling in general. Next, in Section 3, we will describe a brief history of process simulation, and then move on to some specific examples: namely, the construction of a trench isolation region, the exposure and development of a photoresist masking region, and the formation of a BiCMOS structure. Section 4 presents a similar treatment on device behavior simulations. Here, the described examples include: (1) the effect, due to hot electrons, of accumulated charge trapped in the oxide region of a MOSFET device, (2) leakage current in a 3-D cell structure, (3) the "turn-on" characteristics of the corner region of a MOSFET device, (4) simulations of device behavior at room and liquid nitrogen temperatures, and (5) a Monte Carlo electron transport simulation of a MOSFET. Section 5 then turns to the problem of handling the large amount of data generated by these programs, as well as the detailed data required as input to the programs. Here we mention the emerging field of scientific visualization, which is proving to be very

helpful in analyzing the generated data, as well as recent improvements in the geometrical modeling of 3-D structures, which is needed for characterizing complicated device structures. Also, in this section we note the importance of establishing an environment in which the different process and device simulators, and their pre- and post-processing programs, interact with each other and use a common data repository. Finally, Section 6 contains a few concluding remarks.

### 2. BACKGROUND ON SIMULATION FOR SEMICONDUCTOR RELATED PHENOMENA

#### 2.A. Level of physical detail in simulation programs

Our present understanding of the most fundamental microscopic physics involved in semiconductorrelated phenomena is generally considered to be quite accurate. A quantum mechanical description of semiconductor phenomena usually starts with an appropriate "many-body" Hamiltonian. Aside from initial conditions, this Hamiltonian is regarded as containing all of the required information for describing the correlated motion of the electrons and nuclei in a semiconductor material, while under the influence of applied external fields, thermal radiation, and other possible electromagnetic sources. In principle, this information is sufficient for an accurate description of all semiconductor phenomena that enter into semiconductor device fabrication and operation, whether the physical process of concern is, for example, the diffusion of dopant atoms, or the flow of electrons and holes.

Nevertheless, despite what most people regard as a highly accurate understanding of the microscopic physics involved in semiconductor phenomena, considerable limitations are imposed on us when attempting to use this knowledge for predicting more macroscopic physical behavior. Indeed, quantitative descriptions of the complex, correlated motion of the electrons and nuclei are generally quite intractable, without introducing a large number of approximations. Here is where physical models enter: specifically, in order to make approximations, empirical relationships ("laws") and parameters must be introduced. The domain over which these approximations hold, and the range over which the empirical parameters have been measured, then constitute the bulk of the basis for accurate physical descriptions.

Speaking rather loosely, we may view most semiconductor related processes as consisting of the transport of *ions*, *electrons*, and *holes*, as well as their *mixing* behavior, such as occurs in chemical reactions, and in the recombination and generation of electrons and holes. In this way, we may group together much of the following diverse phenomena, such as the conduction of electrons and holes, ion implantation, and the diffusion of dopant atoms within a crystalline structure. Even the oxidation of, for example, silicon, can be similarly characterized, since it involves the chemical reaction of oxygen combining with silicon, and the transport of the chemical reactants and products involved in this process.

Of course, in some semiconductor processes the act of transport is of lesser importance than certain chemical processes, as in the case of the exposure of photoresist materials with light. Also, some problems of interest only involve equilibrium conditions without the flow of particles, as occurs in the stress distribution in a semiconductor structure after oxide has formed, or in the electron concentration and the electrostatic potential distribution in a device when no current is flowing.

Nevertheless, for our present discussion we can use the calculation of transport-related properties to indicate the types of computations, and the various levels of physical approximations, that are typically involved in describing semiconductor-related phenomena. Indeed, let us be even more specific and briefly survey numerical calculations that have been carried out for one particular transport process. By doing so, a clearer picture should form on what we mean by different levels of physical approximations used within the context of numerical simulation. The difference between these approaches essentially lies in the extent to which phenomenological models are incorporated within the calculations.

Although essentially any example will do, let us consider here the case of diffusion of dopant atoms in silicon. We choose this example partly because similar information on other examples, such as electron transport, appears to be more widely known, and partly because diffusion is, indeed, a very important part of semiconductor device fabrication. We emphasize, however, that the general scenario of physical descriptions discussed below for diffusion also holds, more or less, for the other relevant semiconductor phenomena of interest, such as electron transport and ion implantation. Indeed, many different levels of physical accuracy are presently pursued by various researchers attempting to describe and understand the observed behavior of these physical processes. (This point will again be noted in Section 4.A when discussing carrier flow in semi-

The diffusion of impurities in silicon has received considerable attention during the past 30 years or so, due to its technological importance in fabricating silicon-based integrated circuits. The underlying physics is quite complicated, since diffusion necessarily involves the role of defects in the crystalline structure. Consequently, the overall behavior includes the collective interactions of the silicon and dopant atoms, whereby each atom is influenced by the others. In turn, the electronic charge configuration is modified by, and also modifies, the atomic motion.

Some very fundamental computations have been carried out that identify the important mechanisms involved in diffusion processes within silicon. Using

first-principles quantum mechanical calculations involving pseudopotentials[74] and a local-density-functional approximation[75], the total energy has been calculated for different configurations of core electrons and nuclei. Assuming a particular quasistatic change in position of these nuclei, then the total change in energy of the configuration of particles can be found for the particular "path of diffusion" chosen. Detailed calculations were first reported in Refs [76] and [77], while more recent ones are found in Ref. [78].

Calculations such as these are quite interesting and have helped to shed considerable light on mechanisms of diffusion, such as the role played by interstitials and vacancies in diffusion processes[78,79], as well as other possible contributing mechanisms[80]. Nevertheless, such computations are still quite far from actually *simulating* the process of diffusion. More specifically, what we mean here is the capability to calculate the distribution of dopant atoms within silicon at any particular time, and for a variety of physically imposed conditions, such as temperature and initial distribution of dopant impurities.

In order to address this problem, approximations presently need to be made in the physical description of the problem, with empirical relationships and parameters included in the calculations. To obtain time-dependent dynamical properties for the distribution of dopant atoms, "molecular dynamics" calculations[81] have been carried out in such exploratory work as Refs [82] and [83]. Here, the trajectory of the atoms are treated classically, with semi-empirically based interaction potentials between particles. These calculations have shed additional light on the mechanisms of diffusion, such as the dynamical behavior of "jump events" as atoms move through a crystal lattice[84]. Also, this method has provided a classical calculation for atomic relaxation and relaxation energies[85]. Nevertheless, such a simulation approach is still too computationally intensive to give results for use in device fabrication simulation.

Here, we will briefly mention a few other approaches that have been used to simplify the problem still further before turning to the method presently used, nearly to the exclusion of all other methods, by semiconductor device technologists. An interesting Langevin equation approach can be found in Ref. [86] for studying the Brownian diffusion of interstitials in a lattice. More widely pursued simulation methods, with alternative, and additional, physical approximations, involve hopping models[87-91]. These computations generally treat the atoms in a crystal as lying at only specific locations in the lattice, and then describe their motion as a random walk of vacancies and interstitials. Still, despite the simplifying assumptions in this approach, such simulations demand large computational resources, as well as requiring a more accurate characterization than presently exists for the empirical parameters involved in the random walk description.

Consequently, the method most widely used by semiconductor technologists for diffusion process simulation directly entails the numerical solution of a macroscopic equation, i.e. the diffusion equation, which contains empirically based diffusion coefficients. More sophisticated treatments tie together the diffusion of impurities with the diffusion of point defects, by solving a set of coupled partial differential equations[67,92–94] for dopant atoms and point defects. The empirical coefficients here include the diffusion coefficients for each diffusing species and the generation and recombination rates for point defects.

Thus, we see a wide range of approaches to calculating characteristic properties for the single process of diffusion of dopant atoms in a crystalline structure. These approaches do *not* all yield the same information for the diffusion process. Indeed, the first-principles, total-energy-calculation approach yields values for parameters that might be used within a diffusion-equation-solving program, which in turn would be used to predict actual changes in concentration of dopant atoms within a crystalline material.

A major thrust for improving the state-of-the-art simulation of semiconductor-related phenomena is the investigation of how the different simulation approaches properly relate to each other: specifically, under what conditions does one approach become invalid or require modification and, at the other extreme, under what conditions does the extra detail of more first-principles calculations become largely unnecessary?

As emphasized earlier, the situation we have described for simulating the diffusion of dopant atoms in a crystal is very similar to the situation that exists for simulating other semiconductor-related processes, such as ion implantation and the flow of electrons and holes. More specifically, what we mean here is that just as many different levels of physical description are actively being pursued via computational means for studying the diffusion of dopant atoms, so also one can find many levels of physical accuracy that have been investigated via simulation-related methods for the other processes just mentioned. A major dividing line in these computations is the degree to which quantum mechanical effects need to be taken into account in the simulation, and to what extent only classical effects, or semi-classical ones, are adequate. In general, the complexity of computer programs increases as more detailed quantum mechanical effects are taken into account. Of course, as conventional FET and BJT semiconductor devices become smaller, more accurate accounts of quantum mechanical effects become increasingly essential. Indeed, for such novel device structures as described in Ref. [95], quantum mechanical principles are already an essential part of their operation.

Finally, we should note that at whatever level of physical sophistication that is used for a simulation, there exists a wide range of sophistication for the numerical methods by which the computational algorithm can be constructed. Indeed, enormous effort is required in creating algorithms that are as computationally robust and efficient as possible, so as to produce results that numerically converge over a wide range of initial conditions, and yield answers in reasonable amounts of time. The complexity of appropriate numerical algorithms, as well as the ever present limitations imposed by computer resources (i.e. memory and speed), constitute two of the major constraints for obtaining accurate physical descriptions in advanced semiconductor process and device simulation programs.

#### 2.B. Criteria for successful simulation development

Having briefly outlined the different levels of physical detail that one can expect to find in different simulation programs, we will now turn to mention some of the key points that enable successful simulation development within a semiconductor device technology environment. Indeed, over the last decade, improved process and device simulation capability has become increasingly important in the design and development of complex integrated circuits. This increased importance has been primarily due to the growing complexity of semiconductor fabrication processes, ever shrinking device dimensions, and the need to reduce to competitive levels the time and cost associated with VLSI and ULSI design and development.

With the rapid progress in the IC technology, maintaining an advanced and effective simulation capability requires a sustained commitment of resources. There are three main areas that need to be addressed in the development of state-of-the-art simulation: namely, physical model development, software development, and experimental verification.

Indeed, advanced multidimensional process and device simulation calls for models that are comprehensive and physically based. However, this task is usually difficult to achieve, since the physics of many of the processes of interest is quite complicated. In such cases, an alternative is to use empirically based macroscopic models, as discussed in the previous section, with parameters chosen that are related either to experiment, or else to computations that have been carried out with more first-principle microscopic calculations. Such models, while limited in scope, are attractive because they are less computationally intensive than first-principle models. Presently, both complex and computationally intensive first-principle models, as well as simple and empirically based models, play important roles in the simulation of semiconductor related phenomena.

The degree of model complexity forces the simulation algorithms and associated software to be complex. At the same time, advanced software development calls for programs that are numerically robust, modular in nature, optimized in their execution, and easy to learn and use. Particularly from the users' point of view, this latter criteria is one of

the most desirable features that can greatly influence the extent to which a program is used for various applications. As part of this focus, much attention has to be given to pre- and post-processors, data storage and retrieval, and other components that are needed for a complete simulation system.

Finally, a strong experimentation and characterization program is vital to successful process and device model development and verification. Clearly, the predictive capability of any model is a strong function of its foundation in reliable data. Both data generated by modeling experiments as well as technology development efforts need to be considered. From the practical point of view, such data should be readily available, and in a format compatible with each other. An ideal solution is to have a computer-based system where a variety of data and information can be collected and stored in a systematic fashion, and at any point accessed and used with great ease. As an example, a system called BEST[96] has been implemented at IBM and is aiding in both technology as well as process model development and verification efforts. Through this system, data and pertinent information is readily stored and retrieved, and there are also options for their processing and analysis.

The realization of better physical models greatly depends on accurate knowledge of materials and process parameters. The limitations in direct measurement methods for determination of some key parameters is one of the challenges that need to be addressed. For example, measurement techniques for dopant profiling have led to a better understanding and development of models for diffusion and ion implantation. However, all currently used techniques are capable of only measuring 1-D profiles. Nevertheless, there have been recent reports[97,98] that seem promising for quantitative determination of 2-D and 3-D profiles. Such techniques may greatly aid in the development of multidimensional models for ion implantation and diffusion, which will then provide higher accuracy in predicting device structures and their material properties. Using this information in device simulation programs will then yield more accurate predictions for device behavior.

## 3. SIMULATION OF PROCESSES FOR FABRICATION OF SEMICONDUCTOR DEVICES

Here we will first present a brief history on the progress that has been made in simulating semiconductor device fabrication processes, and then indicate some of the key processes that need to be simulated in order to accurately describe device structures. Finally, we will turn to three advanced process simulation examples.

#### 3.A. Brief history of process simulation

The origins of process simulation can be traced to the 1960s. During this period some of the basic process models were developed that in later years were implemented and expanded upon for process simulation. Examples of such early work can be found in Refs [99–104]. These references include work related to modeling of thermal oxidation by the linear-parabolic model[99], ion implantation by the Lindhard–Scharff–Schiott (LSS) theory[100], and dopant diffusion[101–104]. In the area of diffusion, such effects as the built-in electric field[101], segregation during thermal oxidation[102–103], and interactions in multiple-dopant diffusion[104] were considered.

In the 1970s, as in the decade before, the evolution of process simulation was primarily driven by technological needs. Models for processes of interest were extended and refined. In the area of ion implantation, the LSS theory became widely used for describing the ion range distributions in various materials. According to this theory, an ion implant profile may be described to first order by a Gaussian distribution. Range statistics for a variety of ion and target combinations were determined and made available[105,106]. In the area of diffusion, some of the progress dealt with dopant diffusion under extrinsic conditions. Examples of models reported for arsenic, boron, and phosphorus are provided in Refs [107–109] respectively.

With the trend toward smaller devices and more complex processes, a strong need developed to account for what had originally been second-order effects within certain processes. Early models relied primarily on analytical equations, which became inadequate under more complex circumstances. Consequently, numerically based models were necessary for general applicability. The computer implementation of such models led to the development of process simulation programs containing models for a variety of processes. With the introduction of the 1-D simulator SUPREM I[62] in 1977, followed by enhanced versions II[63] and III[64], the concept of a general purpose process simulator for modeling of semi-conductor fabrication steps was established.

Over the last decade, as the shrinking of device dimensions has continued, 2-D process simulation has become a necessity. The origins of 2-D process simulation may be traced to some of the work that was conducted in the 1960s for the analysis of lateral diffusion effects[110,111]. This work represented early attempts at modeling dopant redistribution in 2-D, and led to a better understanding of lateral diffusion near a mask opening for constant-source and instantaneous-source diffusing conditions. While such early 2-D process simulators were relatively simple programs and dealt with only one type of process, they paved the way for modern 2-D process simulation programs.

In the early 1980s, a number of 2-D process simulators were reported[22,112,113]. These simulators primarily focused on modeling of ion implantation, diffusion, and oxidation, and contained fairly basic capabilities for other processes. There were also

596 D. C. Cole *et al.*

some efforts in simulating lithography, etching, and deposition types of processes[47,48]. More recently, there has been an increasing demand for simulators that provide the capability of modeling in a comprehensive manner as many semiconductor processes as possible. This goal can either be achieved by incorporating new features in a simulator, or by establishing links between simulators with different capabilities. An example where a combination of these two options has been adopted is with the process simulator FEDSS[22]. In this case, as the models for ion implantation, diffusion, and oxidation were further developed[23,24], more realistic models for etching and deposition have been added. Moreover, a link has been established with the SAMPLE program[47-52] for lithography simulation. Since SAMPLE also contains models for a variety of etching and deposition processes, these additional models may now be accessed from FEDSS.

#### 3.B. Essential phenomena needed to be described

3.B.1. Ion implantation. Ion implantation is the principal technique for controlled doping of semiconductor devices. For submicron VLSI technologies, where low "thermal budgets" are required to minimize profile broadening by diffusion, correct prediction of ion implanted profiles has become crucial. Analytical models based on a Gaussian or other distribution functions may be used for simulation of ion-implanted profiles. For example, in FEDSS, models based on Gaussian, joined half-Gaussian, and Pearson IV distributions are available for simulation of any element into silicon or into films such as oxide or nitride on silicon. A Gaussian distribution may be used to account for the lateral scattering effects. Specific models for As, P, and B are available. For all cases, angled implants and irregular surface geometries, including undercuts, are allowed.

In addition to analytic implant models, Monte Carlo programs exist for accurately simulating the implantation of ions into semiconductor materials. For example, the TRIM Monte Carlo ion implantation program[25,26] is used within the FEDSS process simulator for 1-D and 2-D implantation in multilayered structures. Such a capability can greatly aid in the understanding of ion implantation (especially lateral scattering in 2-D) and can be used to generate new and improved parameters for analytic models, or to extend their range. Another powerful Monte Carlo program for ion implantation in solids is MARLOWE[114,115]. A desirable feature of MARLOWE is its capability of treating crystalline materials, rather than simply assuming the semiconductor material to be amorphous. Consequently, this program can simulate the channeling of dopant atoms in crystalline materials.

3.B.2. Diffusion. Correct modeling of dopant diffusion is one of the key elements in process simulation for VLSI. Point defects are responsible for most nonequilibrium effects in diffusion, and a

complete diffusion model must be able to account for defect—dopant interactions. Presently, most process simulators model diffusion by a numerical solution of the diffusion equation for dopants, and incorporate nonlinear effects through use of a concentration-dependent dopant diffusivity relationship. Nonequilibrium effects, typically due to thin film/substrate interfacial reactions, are incorporated via boundary conditions. The examples we show later, involving the diffusion of dopant atoms, were obtained via this means with FEDSS.

To directly account for the influence of point defects, the relation for dopant diffusivity may be defined with terms that are dependent on the local concentration of point defects. These in turn can be obtained from the solution of diffusion equations for defects. This approach may be useful for modeling such effects as 2-D oxidation enhanced diffusion of dopants by supersaturation of silicon interstitials[67] (see Ref. [116] for a review on the diffusion of impurities in silicon). Some recent reports also present alternative models with improved degrees of generality in terms of an explicit accounting for the interactions of dopants with point defects[92–94]. The most general form requires the simultaneous solution of a set of nonlinear coupled differential equations for dopants and defects, where the point defect distributions are explicitly calculated. This approach is under development for extensions to FEDSS. Such a simulator will be applicable for modeling a variety of explicit point-defect mediated diffusion effects, such as oxidation enhanced diffusion and nitridation-retarded diffusion. The simulation of rapid thermal annealing (RTA) processes will also require, at the very least, such a formulation, since the short times and high temperatures associated with RTA constitute a highly nonequilibrium state where impurity and point defect "reactions" tend to dominate "diffusion."

3.B.3. Oxidation. Historically, modeling of thermal oxidation of silicon has been based upon the well-known linear-parabolic growth model due to Deal and Grove in 1965[99]. This model is inaccurate in the "very thin" oxide regime (i.e. oxides less than about 20 nm thick). Since this regime has become very important in present day technology, many models have been proposed to account for the growth of thin oxides. In FEDSS, we have chosen two models for the thin-oxide regime: one is an "extension" by J. Slinkman and C. Schaeffer of the work by Deal and Grove that accounts for stress[117], while the other is due to Hu[118].

The problem of modeling oxidation is compounded considerably in 2-D, where one can no longer ignore the mechanical behavior of the growing oxide. Specifically, oxide is known to exhibit fluid flow at process temperatures, but there is currently no consensus as to whether it is viscous, viscoelastic, or even plastic flow[119]. The examples we present shortly are results of FEDSS simulations where the

following models are invoked: the "extended" Deal–Grove growth model[117] and the viscous flow model of Ref. [120] that was modified in Ref. [24]. The oxidation of both silicon and polysilicon are simulated and there is some capability for (empirical) "oxinitridation."

3.B.4. Etching and deposition. The complex nature of material etching and deposition processes has limited the development of physically based models for such processes. Consequently, many simulators, such as FEDSS, include user-defined models for material removal and addition. Presently FEDSS also has a basic etch model that is material-selective and etch-rate sensitive, as well as models for isotropic and anisotropic deposition.

#### 3.C. Trench process simulation

Now let us turn to the first of our examples of semiconductor process related simulations. As will be seen, the example we have chosen involves a large number of process steps (i.e.  $N \gtrsim 50$ ). Moreover, the structure described here represents a technologically important component in the advanced CMOS development of high density DRAMs: namely, the creation of trench structures in silicon[121,122]. Filling these trenches with highly doped polysilicon enables them to be used as storage-capacitor nodes (also see Section 4.C), while an oxide fill provides space conserving isolation regions to be formed between adjacent semiconductor devices (also see Section 4.D).

One of the difficulties involved with fabricating these trench structures is that stress-induced dislocations can form around the trenches. These defects can cause poor device performance, or possibly even an inoperable device. Such dislocations often arise during thermal oxidation, since volume expansion from the reaction at the oxide-silicon interface can create large pressures around the trench structure. To fully understand and prevent such dislocations requires costly and time consuming experimentation. Simulation, as a complementary tool, can greatly aid in reducing the required experimental efforts. An accurate simulation will pinpoint the regions of high stress, as well as enabling the technologist to perform simulation experiments of alternative process steps that might reduce, or even eliminate, these effects.

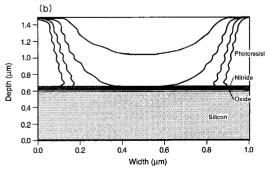

Indeed, using a comprehensive process simulation program, one can simulate a fairly complex structure and analyze stresses that may arise during thermal oxidation, as is shown in the following example. This simulation was carried out using FEDSS. Figure 1(a) shows the mesh generated for a structure of interest that was subsequently used to form a semi-recessed oxide (SROX) region. The structure in Fig. 1(a) consists of a trench formed in silicon, which was first covered by a triple layer of insulators, then filled with polysilicon, and finally covered, as shown, by pad nitride. Figure 1(b) illustrates the simulated structure after oxidation. Here, the computational algorithm

used for simulating the oxidation growth required automatic mesh generation capability[23,24]. A corresponding SEM picture for the actual processed structure is shown in Fig. 1(c). The shape of the simulated SROX compares well with the SEM cross section. Based on simulation, the total SROX thickness is  $0.59 \mu m$ , the lateral "bird's beak" structure is  $0.45 \mu m$ , the distance of the pad nitride wrapage is  $0.26 \mu m$ , and the oxide thickness on silicon is 0.45 µm. These results are in good agreement with the corresponding values of 0.57, 0.45, 0.24, and 0.44  $\mu$ m from the SEM measurement in Fig. 1(c). For the structure in Fig. 1(b), a stress distribution can be calculated. For illustrative purposes, the hydrostatic pressure as calculated by FEDSS is shown in Fig. 1(d) (shear stress components are not shown). The bright green region in the nitride corresponds to high compressive stresses due to the growing oxide. In the vertical bird's beak region, we see that a tensile (bright red) hydrostatic pressure is predominent in the growing oxide due to the oxide volume expansion. However, we note that shear forces can contribute significantly as the oxide flows in this constricted volume region of the bird's beak. The FEDSS simulation predicts high compressive stresses on the surrounding silicon and polysilicon regions. These stresses can contribute to the formation of dislocations in the silicon, which are observed under certain process conditions.

Figures 1(e)–(g) illustrate how a 3-D analysis can be carried out for the previous structure. Figure 1(e) shows the mesh of Fig. 1(a) extruded into the third dimension, with some of the pad nitride layer cut away on the sides. Thus, Fig. 1(a) represents the cross section along points  $A \rightarrow B$  in Fig. 1(e). Taking the cross section along points  $C \rightarrow D \rightarrow E$ , a different oxide growth structure and stress distribution can be examined. Figure 1(f) shows the oxide growth, plus a blowup of the bird's beak on the left-hand side of the trench. The triple layer of oxide–nitride–oxide is visible in the blowup. Figure 1(g) shows the associated hydrostatic pressure plot.

#### 3.D. Lithography simulation

Our second process simulation example deals with lithography. Since the wavelength of visible light is comparable to device dimensions for submicron device structures, then for conventional photoresist exposure methods, the image obtained from a lithographic mask will not match the intended masking design. Moreover, other complicating factors often arise due to topographical variations in the photoresist and in the structures underneath the photoresist. Developing the photoresist introduces another factor that typically offsets the final shape from the intended shape, as well as giving the edge of the photoresist a nonvertical profile.

In order to obtain accurate process simulation capabilities, these factors need to be taken into account since they govern the size and shape of the actual physical mask: namely, the final photoresist structure. The developed photoresist "mask" controls the sections of underlying structures that are eventually oxidized, or subjected to ion implantation, or other processes.

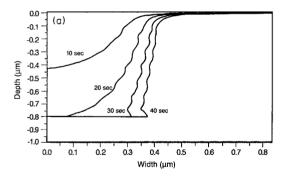

The simulation program SAMPLE [47-52] can be used to predict developed photoresist shapes under various conditions. Here we show an example obtained by linking the SAMPLE and FEDSS simulators together. As can be seen in Fig. 2(a), simulated resist contours were obtained from SAMPLE that corresponds to developments at 10 s intervals. In Fig. 2(b), these contours have been mapped and reflected onto a structure of silicon, oxide, and nitride, which in turn was generated from FEDSS. The meshes associated with these structures are not shown in this figure, but they are shown in Fig. 3. Here, various other options within FEDSS are illustrated for mapping the SAMPLE profiles onto a FEDSS structure, such as positioning the two pieces together, or perhaps extending, or truncating, the end points of the photoresist structure. Control over the generated mesh within the photoresist region, as well as the other regions, is, of course, essential in obtaining accurate simulation results for subsequent process steps.

#### 3.E. BiCMOS structure

Our third process simulation example consists of the construction of a field-effect transistor and a bipolar junction transistor that are placed in close

Fig. 2. Example of FEDSS-SAMPLE lithography simulation. (a) Simulated resist contours from SAMPLE after development at 10-second intervals. (b) Mapped and reflected SAMPLE resist contours on a silicon, oxide and nitride structure generated by FEDSS.

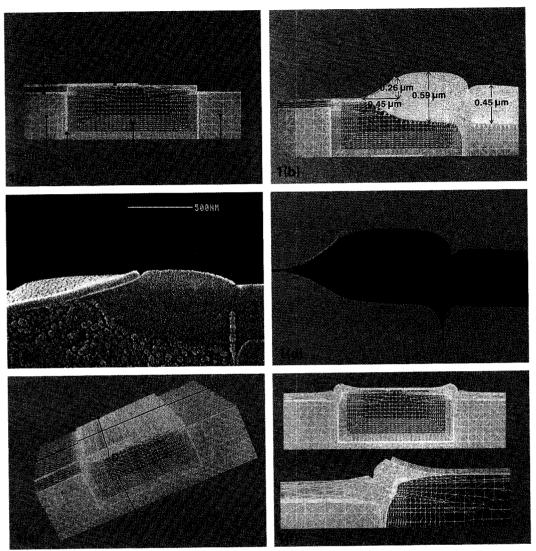

proximity to each other. The inherent complexity associated with the development of the fabrication process for a structure, such as this one, stems in part from the myriad independent parameters involved in each process step. Moreover, fabrication is compounded by the inadequacy of experimental methods to properly characterize impurity distributions in 2 and 3 dimensions. Carefully planned experiments, even when based on statistical arguments, cannot hope to economically provide a complete characterization of device performance as a function of all possible process variations. Simulation can be a very effective complement to experimental work, particularly in the examination of very localized phenomena. Figures 4(a) and (b), for example, depict the results of a partial sequence of simulated process steps that define a local cross section of a typical BiCMOS device structure. The simulated structure shown was constructed using the FEDSS process simulation program.

The initial process simulation step consisted of the growth of an epitaxial layer on a substrate of bare silicon. Implantation of a subcollector then followed. This region is clearly visible as the large red cloud in Fig. 4. An alignment signature was preserved at the appropriate point in the process by exposing the structure to a furnace anneal in an oxidizing ambient. These oxidation steps were accomplished as follows: first, a pad oxide growth was simulated, then a pad nitride deposition, and finally a furnace anneal in the appropriate ambient conditions. For this last step, parameters such as ambient gas (wet or dry O<sub>2</sub>), ambient pressure, HCl content, gas flow rates, time, and temperature, were specified to characterize the process.

Several features of the resulting SROX structures are noteworthy that are predicted by the simulation. For example, a noticeable slope exists between points A and B in Fig. 4. This effect is due to the earlier subcollector oxidation process, which initially caused a slight topographical variation. The close-up of Fig. 4(b) highlights this phenomenon as well as providing a more detailed view of the MOSFET.

A sequence of ion-implantation steps was simulated. The purpose of these steps was to optimize device performance by (1) achieving a low-resistance collector contact, (2) tailoring the FET threshold voltage, and (3) creating lightly-doped source (LDS) and drain (LDD) structures, with halos. Most of the implants were done through oxide layers—sacrificial, gate, or base, as appropriate. The impurity source for the emitter region of the BJT was prepared by first depositing, and then doping, a layer of polysilicon.

Although only a few features of the BiCMOS structure have been highlighted here, this process simulation contains well over 100 distinct process steps that are necessary to accurately characterize the state-of-the-art BiCMOS device structure. Consequently, upon coupling this structure with a device simulation program, enough detail exists within the

Fig. 1. (a) FEDSS mesh for a structure consisting of a trench formed in silicon, covered by a triple layer of insulators, and filled with polysilicon. The top surface is partially covered by pad nitride. (b) FEDSS mesh for the structure shown in Fig. 1(a) after thermal oxidation to form a semi-recessed oxide region. (c) SEM picture for actual semi-recessed oxide region simulated in Fig. 1(b). (d) Simulated hydrostatic pressure distributions in the semi-recessed oxide region at the end of oxidation. High compressive (green) hydrostatic pressure exists in the nitride pad region on top of the lateral bird's beak area, and high tensile (red) hydrostatic pressure exists around the vertical bird's beak region. The maximum compressive and tensile regions are approximately  $10^9$  dynes/cm<sup>2</sup>. These quantities are shown here on a logarithm scale, with 64 separate contours. (e) Here, the 2-D mesh in Fig. 1(a) was extruded into the third dimension, with some of the pad nitride cut away. (f) The top part represents the cross section indicated by points  $C \rightarrow D \rightarrow E$  in Fig. 1(e) after growing oxide for 10 min. The bottom part shows a blowup of the area of interest. (g) The hydrostatic pressure distribution for the bottom part of Fig. 1(f). (See overleaf for Fig. 1(g).)

Fig. 3. Example of FEDSS-SAMPLE mapping options. (a) A mapped, reflected, and meshed structure. (b) Translation of an isolated resist structure. (c) Periodic resist structure generated from translation. (d) This unusual looking structure is shown here to indicate that the user can define his own structure, and can also specify the mesh density in the photoresist structure. The mesh in the photoresist is automatically matched up with the mesh in the semiconductor structure, thereby enabling subsequent process calculations for the two regions.

Fig. 4. BiCMOS cross section generated by FEDSS. (a) An n-MOSFET and a vertical npn BJT are shown. (b) Blowup of the MOSFET to show the source and drain, which contain LDD and LDS/halo structures.

simulated structure to yield the following types of device design information: (1) sensitivity analysis of process ground rules, (2) leakage, (3) breakdown, (4) latchup, and (5) general device performance.

## 4. SIMULATION OF SEMICONDUCTOR DEVICE BEHAVIOR

Our treatment of semiconductor device behavior simulation is similar to the outline of Section 3 on process simulation. First Section 4.A contains background on advances that have been made in device simulation. Sections 4.B-4.G then turn to the parts we mainly want to emphasize in this article: namely, specific pictorial examples of simulations of semiconductor device behavior.

#### 4.A Background on device simulation

Until fairly recently, advances made in the actual simulation of conventional field-effect and bipolar junction transistors have largely been confined to the so-called drift-diffusion (DD) description of electron transport. The equations embodying this description for the flow of electrons and holes in a semiconductor material are given for the 1-D case in Shockley's classic paper in 1949[123], and for the general 3-D case in Shockley's monograph[124] and Van Roosbroeck's article[125], which were both published in 1950. Of course, clear discussions can be found in more recent standard references, such as Refs [126] and [127]. For a concise formulation of the initial DD approach for studying device behavior, see Section 2 of Ref. [128]. Here, the DD relations for the current densities, the current continuity equation, and Poisson's equation, are outlined for this "conventional model", as well as what Ref. [128] terms "auxiliary relations" between the carrier densities and their quasi-Fermi energies, and between the intrinsic Fermi level and the electrostatic potential.

Significant developments leading to, and extending, this DD approach were made by Bardeen and Shockley[129] for a dopant-dependent variable energy bandgap, and Kroemer[130] for recognizing that a position-dependent bandgap would affect the flow of electrons and holes as though "quasi-electric" fields were present. Other advances in accounting for additional physical effects within a DD approach have largely been concerned with heterostructures, more accurate recombination-generation models, Fermi-Dirac statistics for degenerate conditions, some additional high-doping effects, attempts at modeling changes in the effective local mobility at material interfaces, and contact models. Reference [14] describes how some of these effects have been incorporated into a numerical simulation scheme (also see, for example, Ref. [131] and references cited therein). The physical models used in a DD formulation are essentially phenomenological ones, such as mobility and recombination-generation models.

A substantial effort in DD simulation has involved the numerical aspects. Indeed, since carrier concentrations can typically vary by 10–20 orders of magnitude or more in standard semiconductor devices, then a simple linear or polynomial interpolation for discretization of the carrier densities is quite impractical. Instead, the discretization scheme that Scharfetter and Gummel proposed in 1969[132], with some modifications and extensions[131,133], has been the basic approach for simulators today. Even with this scheme, some regions of a device require a very fine discretization, such as in the channel region of an FET, where the carrier density changes dramatically within just 20 nm across the depth of channel.

Apparently the first suggested numerical scheme for solving the DD equations was made by Gummel in 1964[134] for a 1-D analysis of a bipolar transistor. Two-dimensional simulations were developed in the late 60s and early 70s[135–141]. As smaller devices have been made, geometry effects have become increasingly important, thereby necessitating the need for 3-D simulators. Development of such programs were first reported in the early 80s[29,142–143]. (For specific examples where 3-D simulation capability is essential for accurate device characterization of present day technology, see Sections 4.C and 4.D.)

The DD simulation approach has been the main tool for practical device engineering types of application. Indeed, nearly all of industry presently uses the DD method for device analysis of conventional FET and BJT structures. Even for MOSFET device structures with submicron channel lengths of  $0.5-1.0 \mu m$ , the DD method can yield satisfactory analysis of many aspects of device behavior, such as the source-to-drain current as a function of applied biases, and estimates of leakage currents. For typical simulation examples of devices of these sizes, improvements beyond the DD method are not usually the most significant factor for obtaining sensibly accurate simulation results. Instead, other critical factors exist, such as a close characterization of doping profiles and of material interface properties.

Nevertheless, the physics embodied by the DD approach is limited. Developing the next generation of simulation capability demands considerable work. Hence, we presently see the situation where the literature contains numerous papers on the development of simulation methods that are physically more accurate than the DD method. Here, a major concern is making these new programs numerically robust, and in keeping the computational time down so as to remain practical for multiple simulation runs of semiconductor devices. Undoubtedly, as device sizes continue to shrink, these methods will eventually become essential for all of industry in general.

An improved physical description over the DD method becomes increasingly critical as silicon based device dimensions approach  $0.25 \,\mu\text{m}$ , and smaller, in order to account for effects such as velocity

D. C. Cole et al.

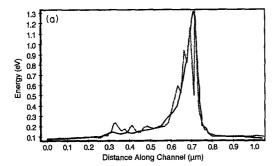

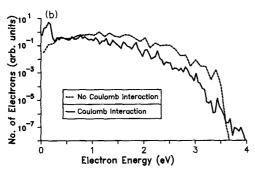

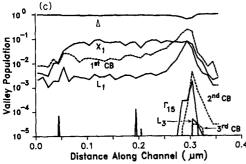

overshoot. Also, quasi-ballistic transport becomes important for MOSFETs with channel lengths below about 0.10 µm. Indeed, even for much longer channel-length devices, an accurate description of the energy and velocity distribution of electrons throughout the device certainly requires more than just the usual DD description coupled with the common assumption of a drift-Maxwellian velocity distribution. Detailed band-structure effects are required to properly characterize the energy distribution of carriers far away from the valleys and peaks in the conduction and valence bands[43]. Moreover, high electric fields can occur over fairly short distances in even conventional MOSFETs with channel lengths of 1 µm or more, as in the case when pinch-off conditions occur. Indeed, a distance of 20 nm is not an uncommon length for the width at half-maximum of the peak of the electric field component along the channel, just at the onset of pinch-off conditions. Also, the average current flow usually curves away from the Si/SiO2 interface and then curves into the heavily doped drain pocket (see the illustration in Fig. 5a). Since the drain region in conventional MOSFETs often has effective junction widths around 50 nm, or smaller, large electric fields can exist in these regions that give rise to high energy carriers. (See, for example, Fig. 20a, which gives the energy distribution of electrons in a 0.35-µm channel length n-MOSFET. Here, much of the high-energy region of the electrons lies along the edge of the drain pocket.)

Thus, even for a MOSFET with a channel length of  $1 \mu m$  or more, we can expect that there will be small, but critical, regions within the device in which the electron distribution will be altered from a simple drifted-Maxwellian velocity form. Within these regions, highly energetic carriers can result in carrier transport up into the gate oxide, or cause a sufficient number of impact ionization events to yield significant substrate current. As discussed by Barker[144], we expect that the full Boltzmann transport equation is necessary for accurate descriptions of the complete behavior of submicron devices (i.e. the accurate calculation of quantities like gate and substrate currents for MOSFETs and the calculation of general device behavior during fast switching conditions), and that even the Boltzmann equation may not be fully satisfactory for device scales below  $0.25 \mu m$ .

Of course, most macroscopic device properties can certainly still be simulated with the DD method, or by modifications of this method, without necessarily solving the full Boltzmann equation. Parameterized phenomenological models, such as the mobility model[145–152], enable some shortcuts to be made. However, the details of the energy distribution, and even the precise carrier density (e.g. including an energy balance equation alters the calculated carrier density[57]), are simply not available without more sophisticated treatments.

In what follows, we outline some of the research to date on methods that go beyond the DD approach,

in order to provide a flavor for the motivations, concerns, and focus in such activities today. Most work on improving the physical description for conventional device simulation has centered on the Boltzmann transport equation, which represents a semiclassical description of carrier transport. Quantum mechanical effects enter via the effective masses of the carriers, which depend on the carrier momentum, and via the scattering mechanisms. Otherwise, the carriers are treated within this description as classical charged particles following Newton's equation of motion.

In 1962, Stratton[153] made a significant contribution toward a better physical description of carrier transport, as well as an improved understanding of the relationship between the DD description and the more accurate Boltzmann equation description. Bløekjær[154] improved the theory further in 1970 and helped point the way toward what is now often referred to as the "hydrodynamical model" for carrier transport. This method involves multiplying the Boltzmann equation by successive powers of components of the velocity vector, and then calculating expectation values for all terms so as to yield relationships between moments of the velocity components. The resulting equations are essentially the Euler equations, as described in, for example, Refs [155] and [156]. The full set of velocity moments yields the complete electron velocity distribution. Dealing only with moments up to the second power, as presently done in most hydrodynamical models. means that approximations need to be made to produce phenomenological models for the remaining higher-order moments in the transport equations.

Cook and Frey[157] showed a clear set of assumptions that relate the DD approach to the Boltzmann equation. Further significant work on the hydrodynamical model can be found in Refs [158–165], with much of the attention focusing on improved numerical discretization schemes for handling the additional higher-moment terms.

Besides work on the hydrodynamical model, much has been accomplished by researchers on solving the full Boltzmann transport equation for device structures of interest. The main numerical approaches have been iterative and Monte Carlo methods. References [166–168] review numerical and analytical work on the Boltzmann equation up until the early 1980s. Since that time, the Monte Carlo method has clearly been the dominant focus in research activity. References [169–171] review this method.

The Monte Carlo method for solving the Boltzmann equation is similar to the molecular dynamics approach[81] described in the discussion on diffusion in Section 2.A. More specifically, however, the trajectories of electrons and holes are followed in space while under the influence of applied electric fields. Probabilities are calculated for scattering events due to phonons, carrier—carrier interactions, ionized and neutral impurities, and surface scattering at interfaces

between the different types of materials. These scattering events are treated as introducing instantaneous changes in the carrier trajectories. Impact ionization and the recombination—generation of electrons and holes can also be taken into account in a probabilistic manner. By summing over a large number of carrier trajectories, statistical results can be obtained that describe the energy and momentum distribution of carriers at each point in space within a device structure.

Fairly recently, the Monte Carlo simulation program called DAMOCLES was developed by M. Fischetti and S. Laux. For a detailed description of the physics embodied in this program, as well as new results for submicron device behavior, see Refs [43-46]. The program DAMOCLES has been used to simulate the behavior of 2-D device structures including both FETs and BJTs. Besides conventional silicon based devices, DAMOCLES can handle some heterostructure devices. Significant features of this program are that carrier-carrier interactions are taken into account, and Poisson's equation is solved self-consistently with the Monte Carlo part of the program. This program significantly advances the state-of-the-art in device modeling because it incorporates a full band structure for the carriers, along with statistical enhancement features for aiding the calculation of statistically rare events. Consequently, the program can simulate the behavior of carriers that are sufficiently energetic to lie far from the minimum and maximum in the first conduction and valence bands, as well as carriers that lie within higher-order energy bands. These regions are typically the important ones for giving rise to interesting hot-electron effects, as exhibited by gate and substrate currents in MOSFETs. Section 4.G describes an example of a simulation of a MOSFET using DAMOCLES.

Although much of the present interest in such Monte Carlo simulations lies with investigating the full behavior predicted by Boltzmann's transport equation, considerable interest also exists in reducing the enormous CPU times required by this method. Here we mention Refs [172] and [173], as well as a number of references cited in Ref. [173] that have explored more approximate, but faster, variations on the strict Monte Carlo approach.

Finally, we want to mention here the significant work that has been done by a large number of researchers on yet further improvements in the physical descriptions of charge-carrier transport in semiconductors than is provided by the semiclassical Boltzmann transport equation. For example, advances have been made in describing quantum-size effects, such as occur in the inversion and accumulation layers at semiconductor-insulator interfaces, heterojunctions, and quantum wells. Such problems have been treated in various simulation work by taking the one-electron Schrödinger equation into account[174]. Quantum interference effects and other

related topics of interest are discussed by Datta in Ref. [175]. Finally, significant work has been done involving quantum transport theory; Refs [176] and [177] contain reviews of this field. A recent example of simulation results involving quantum transport theory, which was applied to different materials, is reported by Brunetti et al. in Ref. [178]. For an elementary introduction to computer simulation of quantum transport and tunneling, see Barker's discussion in Ref. [179].

Thus, as discussed in Section 2.A, many levels of physical accuracy are presently being researched for simulation-related work on carrier transport. We now turn to examples of simulation that we have used in our own work involving conventional FET and BJT device structures. Consequently, our focus is mainly on the more macroscopic DD description of carrier transport which, as discussed earlier, is adequate for predicting the general behavior of all but the most experimental of such structures in industry today. As will be seen, the 3-D aspects of conventional devices introduce many interesting issues that can be explored by DD simulation methods. We also report on some low-temperature simulation work via this method. Our final example in Section 4.G contains a simulation based on the more fundamental physical description of the semiclassical Boltzmann transport equation.

#### 4.B. Some early examples of device simulation

The continuing efforts by device designers to shrink feature sizes has historically been marked by the discovery, and subsequent solution, of myriad problems. Simulation has helped to understand and characterize some of the problems, thereby enabling superior device designs to be realized. A typical problem solved by early 2-D device simulations using the DD method involved the so-called "short-channel" effect, so that threshold-voltage values and transconductance characteristics could be accurately calculated when long-channel analytic formulae were no longer applicable (see, for example, Ref. [140]).

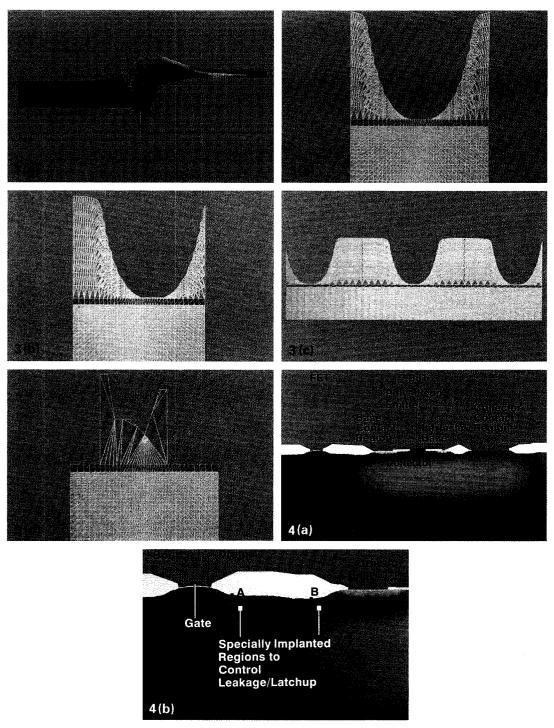

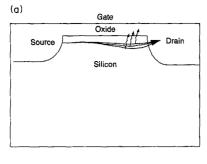

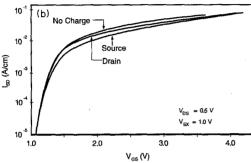

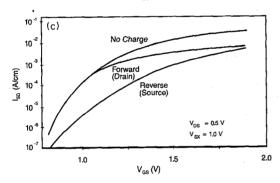

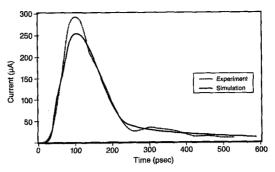

Another set of problems that was more difficult to characterize was due to so-called "hot-electron" effects. Such problems increasingly became more of a concern in the late 70s as device dimensions were scaled without proportionate reductions in powersupply voltage. Observed performance degradation (e.g. substantial gate and substrate currents, threshold-voltage shifts, and decreased transconductance) in MOSFET structures of the kind shown in Fig. 5(a) was hypothesized at the time to be due to high-energy carriers resulting from strong electric fields in the vicinity of the drain, so that carriers could be injected into, and trapped within, the gate insulator. Figure 5(b) shows an example of typical experimental data that were found to result from operating devices under high bias conditions. The curve labeled no charge represents sourceto-drain current vs gate potential, prior to charge

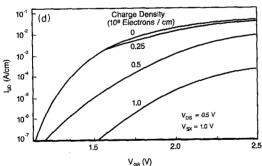

Fig. 5. Effects of charge trapped in the gate insulator. (a) Standard MOSFET. Hot electrons are injected into gate near the drain. (b) Experimental results. (c) Simulated results. (d) Results predicted by simulation for change in  $I_{\rm SD}$  vs  $V_{\rm GS}$ , due to change in fixed charge in oxide.

accumulating in the oxide, while the *drain* curve is the result obtained after the device was operated for a sufficiently long time for accumulation to occur. The *source* curve differs from the *drain* curve in that the bias between source and drain was reversed.

An accurate description of hot-electron behavior is now only becoming available with relatively recent advances made with Monte Carlo simulations (see

Section 4.G). However, DD simulations carried out in the 70s were able to address certain aspects of hot-electron effects. For example, as described in Refs [180] and [181], the FIELDAY program was used to simulate the effect on device characteristics, as shown in Fig. 5(c), of introducing fixed charge into the oxide. As can be seen, good qualitative agreement was obtained between the experimental data of Fig. 5(b) and the simulation results of Fig. 5(c), thereby helping to affirm device designers' hypothesis of the source of the change in device characteristics. The utility with which a variety of process variations were able to be studied proved indispensable in the effort to optimize the performance of the structure. An example of the kind of rapid parametric investigations afforded by simulation is shown in Fig. 5(d), where the effects are illustrated of different magnitudes of fixed charge near the heavily doped source pocket.

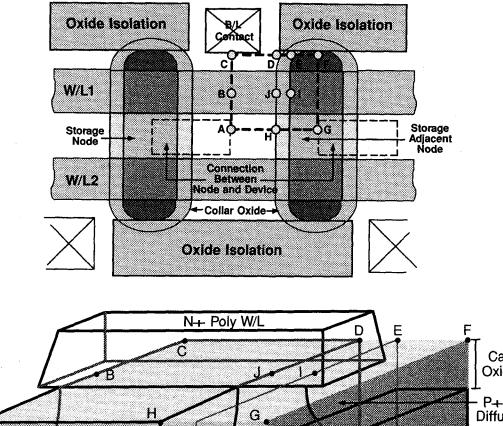

## 4.C. Three-dimensional device modeling of a parasitic leakage mechanism in a 16-Mb DRAM cell

Here we describe an example where 3-D modeling capability was essential for accurately predicting device-related behavior. This example involves the simulation of leakage current from the storage node of a particular 16-Mb DRAM cell design that has been described elsewhere in the literature[182].

A top view of a portion of the memory array layout is drawn in Fig. 6. As can be seen, the overall cell structure is fairly complicated, and requires detailed modeling of the structure to predict actual device behavior. Between adjacent cells, oxide isolation regions serve to block possible conduction paths. The node of the storage capacitor for each cell is formed by first etching a deep trench into the silicon substrate. The trench is then lined with an insulator and filled with heavily doped polysilicon. The silicon substrate acts here as an effective capacitor plate that mirrors the charge on each polysilicon storage node, while a conducting bridge provides electrical continuity between the access transistor and the storage capacitor. The cell can be addressed by electrically selecting the bit line and word line that cross at the desired location in the memory array.

Even though the top portion of the perimeter of the storage trench is lined with a fairly thick layer of isolation oxide, which is referred to here as the collar oxide, there is some interaction between the storage node polysilicon and the adjacent transistor. Indeed, the state of the signal on the storage capacitor affects the characteristics of the transistor. One way of viewing the influence of the storage capacitor on the transistor's behavior is that the top portion of the storage node polysilicon acts as an effective gate on the parasitic FET that exists between the node and bit line diffusions.

To account for the effect of the presence of the trench capacitor on leakage current, the FIELDAY program was applied to the region enclosed by the (a)

(b)

A P+ Node Diffusion

N - Well

Node Dielectric

Fig. 6. (a) Top view showing modeled region. (b) Perspective view of modeled structure. In these figures, B/L and W/L refer to "bit line" and "word line", respectively.

dotted box in Fig. 6(a). A perspective drawing of this region is given in Fig. 6(b). The letters A, B, ..., denote points in common between Figs 6(a) and (b). A finite element mesh was constructed so that a numerical solution could be obtained by the DD semiconductor set of equations. Part of this 3-D mesh

is shown in Fig. 7(a), with the remainder of the mesh cut away for viewing purposes. Again, the letters A, B, ..., in this figure correspond to the points shown in the previous figures.

Different mesh densities were used in order to obtain an estimate on numerical accuracy of

simulated results. The mesh sizes used here ranged from 6000 to 30,000 nodes. For a mesh with 20,000 nodes, the simulation time was about 10 CPU min per bias point on an IBM model 3090/600E computer running as a uniprocessor.

Figure 7(b) is a color plot of the doping concentration for the same mesh region shown in Fig. 7(a), while Fig. 7(c) illustrates the hole-minus-electron concentration under bias conditions that were found to yield the largest leakage current due to the presence of the adjacent storage node in a low-level state. The oxide region (yellow) closest to the observer has been cut away to reveal the underlying silicon. As can be seen, a conduction path forms along points H and J. This path continues over to point D, although this portion of the path is hidden from sight here because of the presence of the oxide region that has not been removed for viewing.

Our 3-D modeling of this 16-Mb cell clearly showed that the worst-case electrical biasing configuration for leakage occurred in the case of a stored high-level leaking down. With the node at a high level and the bit line diffusion at ground, the drain-tosource voltage, and hence the drain-induced barrierlowering effect, is maximized. In this case, the parasitic leakage is gated by the polysilicon storage node connected to the adjacent device. Since the node of the device being studied is at a high level, the parasitic mechanism occurs on one sidewall only. On the other hand, the electrical biasing configuration for a low-stored level leaking up produces less leakage current despite parasitic conduction occurring on both sides of the device. In this situation the node itself and the node of the adjacent device are low, but the drain-to-source voltage is less than with the worst-case leakage configuration, since the storage nodes are written to approximately one threshold-voltage drop above zero.

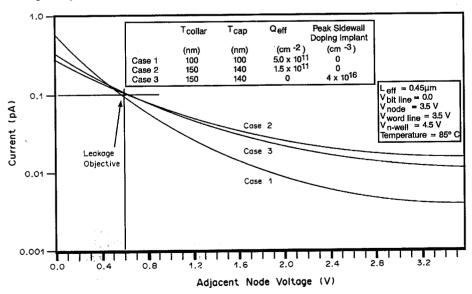

Thus, 3-D modeling has shown that drain-induced barrier lowering has a significant effect on sidewall parasitic leakage. Moreover, the use of simulation has identified device parameters offering significant leverage in reducing leakage from this mechanism. Variations in temperature, trench sidewall fixed charge, doping profiles, trench isolation oxide thickness, trench polysilicon recess depth, channel length and *n*-well back bias have all been investigated. Figure 8 shows modeled device-leakage characteristics for three variations in physical parameters. This plot demonstrates that many options are available for meeting the leakage objective.

Good agreement with experimental data has also been obtained. Figure 9 compares the modeled and measured locus of points in the "adjacent trench voltage-channel length" plane that meet the leakage objective of 0.1 pA. As can be seen, agreement is good.

4.D. Three-dimensional device modeling of oxidefilled-trench isolation bounded MOSFETs at room and liquid nitrogen temperatures

This section describes a second simulation of a MOSFET that required a 3-D modeling capability. Moreover, the following simulation includes results that clearly illustrate the significantly different behavior of typical devices at room and low temperatures.

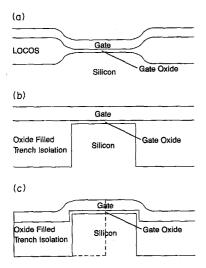

As device sizes decrease, isolating devices from one another becomes more difficult. For dimensions below one micron, a significant limiting factor for developing smaller devices has been the so-called "bird's beak" that is due to the encroachment of the local oxidation of silicon (LOCOS)[183] isolation regions into active device regions. This effect causes thicker oxide in the active device region, thereby hampering device performance. In addition, dopant atoms migrate under the LOCOS into the device areas, further affecting the device behavior. An alternative approach involves etching a trench and filling

Fig. 8. Modeled leakage characteristics.

Fig. 7. (a) Finite-element mesh for model. Blue is silicon, yellow is oxide. Oxide has been removed from the portion closest to the observer for viewing underlying silicon. (b) Doping concentration. Green is p-type, red is n-type silicon. (c) Hole minus electron concentration showing formation of parasitic conduction path on trench sidewall.

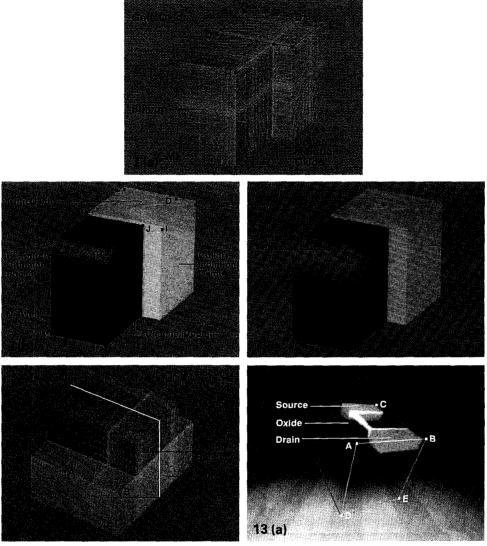

Fig. 11. A typical 3-D mesh used for device modeling: gray—silicon; yellow—oxide; blue—polysilicon; red—nitride. The points A, B, ..., E correspond to the same points in Fig. 13(a). The cross section indicated by the bright white line represents the left-hand side of the device sketched in Fig. 10(c).

Fig. 13. Electron density in a trench-isolated MOSFET, showing turn-on as the gate bias is increased from (a) to (c). Note that the device corner inverts at a lower gate bias than does the planar region. (See overleaf for Figs 13(b) and (c).)

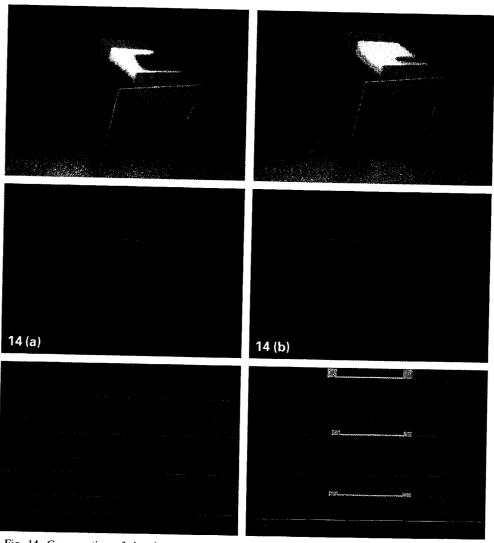

Fig. 14. Cross section of the electron density at mid-channel with the gate bias as the third axis. (a) T = 300 K. (b) T = 77 K.

Fig. 15. A sequence of contour plots of electron charge concentration that illustrate the evolution of the electron charge concentration after an  $\alpha$ -particle strike. The right-hand side of each of the four plots represent the region where the pn junction lies. The  $\alpha$ -particle enters from the right-hand side. The top cross section shows the initial situation before the  $\alpha$ -particle hits. The next cross section down indicates the electron charge distribution 3 ps after the  $\alpha$ -particle strike, while the next two cross sections show the situation at 90 and 180 ps, respectively.

Fig. 18. Simulation using FIELDAY to illustrate the effects of impact ionization and incomplete ionization for a 0.35- $\mu$ m channel length n-MOSFET device with LDD structure. (Top) Doping concentration. Red is n-type, green is p-type silicon. (Middle) and (lower) Hole concentration at 77 K, for  $V_{DS} = 2.0$  V,  $V_{GS} = 4.0$  V, and  $V_{SX} = 0.0$  V. (Middle) Simulation assuming complete ionization. (Lower) Simulation with incomplete ionization model.

Fig. 9. Comparison of model data.

it with oxide to provide isolation[122]. This shallow trench isolation (STI) approach has been demonstrated to be a feasible technology for submicron isolation, as it eliminates the bird's beak. However, the simulation described here shows that device behavior changes due to this new approach to isolation.

For devices isolated from each other via a LOCOS structure, a polysilicon gate that passes across the device will curve upward and away from the device once it reaches the isolation oxide, as shown in Fig. 10(a). This figure represents the cross section of the region under the gate of a MOSFET, where the source and drain of the device are situated above and below Fig. 10(a). For this particular configuration of the polysilicon gate, the portion of the gate over the LOCOS region will have little effect upon the device behavior. Consequently, a simple 2-D simulation will give an adequate description of the behavior of the device, where the 2-D region is taken in the plane perpendicular to Fig. 10(a) and along the axis of the device, so that it includes the source and drain regions. (Of course, if a very narrow LOCOS structure is used, the encroachment of the bird's beak

Fig. 10. Cross section through MOSFET structures at mid-channel, perpendicular to the channel axis: (a) LOCOS, isolated device; (b) trench-isolated device; (c) trench-isolated device with isolation oxide recess and gate wraparound. The left-hand side of the device in Fig. 10(c), which is enclosed by the dashed line, represents the cross section region indicated in Fig. 11 by the bright white line.

discussed above results in a non-uniform oxide thickness across the channel. This so-called "narrow-channel effect" would require 3-D modeling in order to adequately simulate the device behavior. In this case, the threshold voltage increases with decreasing channel width. However, such structures are undesirable and are generally not used, so we will not address this point any further here.)

In the case of an STI-bounded device, the gate runs flat across the isolation, as shown in Fig. 10(b). Consequently, the part of the gate over the STI region creates more of a fringing effect on the corner and sidewall of the silicon mesa[184–186] than in the LOCOS case in Fig. 10(a). This edge effect becomes even stronger if the isolation region is partly eroded away, so that the gate wraps around the corner of the device mesa as in Fig. 10(c)[186, 187]. Now, the regions of the channel near the edges of the device mesa will behave much differently than the region at the center of the mesa. Consequently, 3-D modeling is required to accurately simulate the device characteristics.

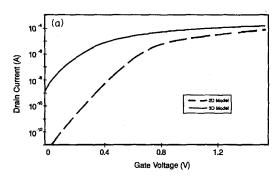

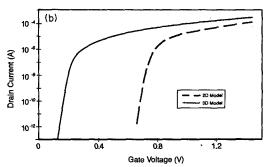

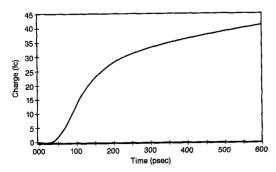

The objective of the device simulation to be described here was to study the current turn-on behavior of trench-isolated devices in which the corner effects described above are clearly important. To carry out this task, a 3-D mesh was constructed for use in the FIELDAY device simulator[29], as shown in Fig. 11. This mesh contained approximately 30,000 nodes and 60,000 elements.