### **BOSTON UNIVERSITY**

## COLLEGE OF ENGINEERING

Dissertation

# MODELING AND OPTIMIZATION OF EMERGING ON-CHIP COOLING TECHNOLOGIES VIA

### **MACHINE LEARNING**

by

## **ZIHAO YUAN**

B.S., Central Michigan University, 2015 M.S., University of Southern California, 2017

Submitted in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

2022

© 2022 by ZIHAO YUAN All rights reserved

## Approved by

First Reader

Ayse K. Coskun, PhD Interim Associate Dean of Educational Initiatives Professor of Electrical and Computer Engineering

Second Reader

Sherief Reda, PhD Professor of Engineering and Computer Science Brown University

Third Reader

Ajay Joshi, PhD Professor of Electrical and Computer Engineering

Fourth Reader

Rabia Yazicigil, PhD Assistant Professor of Electrical and Computer Engineering

The greatest challenge to any thinker is stating the problem in a way that will allow a solution.

- Bertrand Russell

### Acknowledgments

First, I would like to express my most profound appreciation to my advisor, Prof. Ayse Coskun. This work would not have been possible without her help and support. Her guidance and encouragement allowed me to turn this work into multiple conference and journal papers. I am thankful to Prof. Sherief Reda and Prof. Evelyn Wang, who provided substantial guidance to my research. My sincere thanks must also go to my committee members, Prof. Ajay Joshi and Prof. Rabia Yazicigil. They generously gave their time to offer me valuable suggestions and feedback. I wholeheartedly thank my parents, Lixiu Wang and Tianbo Yuan, for their trust, encouragement, and patience. Without their love and support, this dissertation would not have been possible.

I want to thank my collaborators, Prachi Shukla, Geoffrey Vaartstra, Sofiane Chetoui, Sean Nemtzow, Carlton Knox, and Mostafa Said, for supporting me with their expertise and intuition and helping me to solve scientific and technical problems.

I also appreciate the support and help from my colleagues and alumni in our research group: Tiansheng Zhang, Fulya Kaplan, Emre Ates, Onur Sahin, Yijia Zhang, Aditya Narayan, Burak Aksar, Mert Toslali, Daniel Wilson, and Anthony Byrne, Efe Sencan. There is no way to express how much it meant to me to have been a member of the Performance and Energy-Aware Computing Laboratory (PeacLab). These brilliant colleagues and friends inspired me and brought fun and happiness throughout my PhD student life. My appreciation also goes to my friends and colleagues from Integrated Circuits and Systems Group (ICSG) and Computer Architecture and Automated Design Lab (CAAD) at Boston University.

I thank Ankush Varma for the internship opportunity at Intel, and I am grateful for the experience. I also thank Palit Nilanjan, Ujjwal Gupta, and Nikethan Baligar for mentoring me during my internship at Intel. I can confidently say I have grown and learned under

their mentorship.

In this thesis, some parts of the contents in Chapter 2 are reprints of the material from the following paper:

Zihao Yuan, Sherief Reda, and Ayse K. Coskun. Compact Thermal Modeling of Emerging Cooling Technologies for Processors. To appear in *Embedded Cooling* of Electronic Devices Book. Editors: Madhu Iyengar and Mehdi Asheghi. World Scientific Publishing Company (WSPC), 2022.

Some parts of the contents in Chapter 3 are reprints of the material from the following papers:

- Zihao Yuan, Prachi Shukla, Sofiane Chetoui, Sean Nemtzow, Sherief Reda, and Ayse K. Coskun. PACT: An Extensible Parallel Thermal Simulator for Emerging Integration and Cooling Technologies. In *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 41, no. 4, pp. 1048-1061, April 2022.

- Zihao Yuan, Tao Zhang, Jeroen Van Duren, and Ayse K. Coskun. Efficient Thermal Analysis of Lab-Grown Diamond Heat Spreaders. In Proceedings of ASME International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems (InterPACK), Nov. 2021.

Some parts of the contents in Chapter 4 are reprints of the material from the following papers:

Zihao Yuan, Geoffrey Vaartstra, Prachi Shukla, Mostafa Said, Sherief Reda, Evelyn Wang, and Ayse K. Coskun. Two-Phase Vapor Chambers with Micropillar Evaporators: A New Approach to Remove Heat from Future High-Performance Chips. In Proceedings of *19th IEEE Intersociety Conference on Thermal and Thermomechnanical Phenomena in Electronic Systems (ITHERM)*, pp. 456-464, May 2019.

- Zihao Yuan, Geoffrey Vaartstra, Prachi Shukla, Sherief Reda, Evelyn Wang, and Ayse K. Coskun. Modeling and Optimization of Chip Cooling with Two-Phase Vapor Chambers. In Proceedings of *IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED)*, pp. 1-6, Jul. 2019.

- Zihao Yuan, Geoffrey Vaartstra, Prachi Shukla, Zhengmao Lu, Evelyn Wang, Sherief Reda, and Ayse K. Coskun. A Learning-Based Thermal Simulation Framework for Emerging Two-Phase Cooling Technologies. In Proceedings of *Design, Automation and Test in Europe (DATE)*, pp. 400-405, 2020.

- Carlton Knox, Zihao Yuan, and Ayse K. Coskun. Machine Learning and Simulation Based Temperature Prediction on High-Performance Processors. To appear in ASME International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems (InterPACK), 2022.

Some parts of the contents in Chapter 5 are reprints of the material from the following papers:

- Zihao Yuan, Geoffrey Vaartstra, Prachi Shukla, Sherief Reda, Evelyn Wang, and Ayse K. Coskun. Modeling and Optimization of Chip Cooling with Two-Phase Vapor Chambers. In Proceedings of *IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED)*, pp. 1-6, Jul. 2019.

- Zihao Yuan, Geoffrey Vaartstra, Prachi Shukla, Zhengmao Lu, Evelyn Wang, Sherief Reda, and Ayse K. Coskun. A Learning-Based Thermal Simulation Framework for Emerging Two-Phase Cooling Technologies. In Proceedings of *Design, Automation and Test in Europe (DATE)*, pp. 400-405, 2020.

- Zihao Yuan and Ayse K. Coskun. Neural Network-based Cooling Design for Highperformance Processors. In *iScience*, vol. 25, no. 1, pp. 103-582, Jan. 2022.

As part of this thesis, the work above has been partially funded by NSF CRI (CI-NEW) grant #1730316/1730003/1730389, NSF CCF grant #1910075/1909027, Diamond Foundry, and Boston University's Undergraduate Research Opportunities Program.

# MODELING AND OPTIMIZATION OF EMERGING ON-CHIP COOLING TECHNOLOGIES VIA MACHINE LEARNING

## **ZIHAO YUAN**

Boston University, College of Engineering, 2022

Major Professor: Ayse K. Coskun, PhD Interim Associate Dean of Educational Initiatives Professor of Electrical and Computer Engineering

### ABSTRACT

Over the last few decades, processor performance has continued to grow due to the downscaling of transistor dimensions. This performance boost has translated into high power densities and localized hot spots, which decrease the lifetime of processors and increase transistor delays and leakage power. Conventional on-chip cooling solutions are often insufficient to efficiently mitigate such high-power-density hot spots. Emerging cooling technologies such as liquid cooling via microchannels, thermoelectric coolers (TECs), twophase vapor chambers (VCs), and hybrid cooling options (e.g., of liquid cooling via microchannels and TECs) have the potential to provide better cooling performance compared to conventional cooling solutions. However, these potential solutions' cooling performance and cooling power vary significantly based on their design and operational parameters (such as liquid flow velocity, evaporator design, TEC current, etc.) and the chip specifications. In addition, the cooling models of such emerging cooling technologies may require additional Computational Fluid Dynamics (CFD) simulations (e.g., two-phase cooling), which are time-consuming and have large memory requirements. Given the vast solution space of possible cooling solutions (including possible hybrids) and cooling subsystem parameters, the optimal solution search time is also prohibitively time-consuming. To minimize the cooling power overhead while satisfying chip thermal constraints, there is a need for an optimization flow that enables rapid and accurate thermal simulation and selection of the best cooling solution and the associated cooling parameters for a given chip design and workload profile.

This thesis claims that combining the compact thermal modeling methodology with machine learning (ML) models enables rapidly and accurately carrying out thermal simulations and predicting the optimal cooling solution and its cooling parameters for arbitrary chip designs. The thesis aims to realize this optimization flow through three fronts. First, it proposes a parallel compact thermal simulator, PACT, that enables speedy and accurate standard-cell-level to architecture-level thermal analysis for processors. PACT has high extensibility and applicability and models and evaluates thermal behaviors of emerging integration (e.g., monolithic 3D) and cooling technologies (e.g., two-phase VCs). Second, it proposes an ML-based temperature-dependent simulation framework designed for twophase cooling methods to enable fast and accurate thermal simulations. This simulation framework can also be applied to other emerging cooling technologies. Third, this thesis proposes a systematic way to create novel deep learning (DL) models to predict the optimal cooling methods and cooling parameters for a given chip design. Through experiments based on real-world high-power-density chips and their floorplans, this thesis aims to demonstrate that using ML models substantially minimizes the simulation time of emerging cooling technologies (e.g., up to  $21 \times$ ) and improves the optimization time of emerging cooling solutions (e.g., up to  $140 \times$ ) while achieving the same optimization accuracy compared to brute force methods.

# Contents

| 1 | Intr | oductio  | n                                                       | 1  |

|---|------|----------|---------------------------------------------------------|----|

|   | 1.1  | Motiva   | ation and Key Contributions                             | 1  |

|   | 1.2  | Disser   | tation Organization                                     | 7  |

| 2 | Bac  | kgroun   | d and Related Work                                      | 8  |

|   | 2.1  | Comp     | act Thermal Modeling Methodology                        | 8  |

|   | 2.2  | Emerg    | ing Cooling Technologies and CTMs                       | 9  |

|   |      | 2.2.1    | TECs                                                    | 10 |

|   |      | 2.2.2    | Liquid Cooling via Microchannels                        | 13 |

|   |      | 2.2.3    | Hybrid Cooling                                          | 15 |

|   | 2.3  | Coolir   | ng Optimization Methods                                 | 17 |

| 3 | Ena  | bling Fa | ast and Accurate Parallel Thermal Simulations with PACT | 18 |

|   | 3.1  | Introd   | uction                                                  | 18 |

|   | 3.2  | Backg    | round of Existing Compact Thermal Simulators            | 22 |

|   | 3.3  | Propos   | sed SPICE-Based Thermal Simulator                       | 24 |

|   |      | 3.3.1    | PACT Simulation Flow                                    | 25 |

|   |      | 3.3.2    | Thermal Netlist and SPICE Circuit Components            | 26 |

|   |      | 3.3.3    | Extensibility of PACT                                   | 28 |

|   |      | 3.3.4    | Compatibility of PACT                                   | 34 |

|   |      | 3.3.5    | OpenROAD Interface                                      | 34 |

|   |      | 3.3.6    | PACT Solver                                             | 36 |

|   | 3.4  | Experi   | imental Results                                         | 39 |

|   |     | 3.4.1   | Speed Analysis with Complex 2D and Monolithic 3D ICs            | 40    |

|---|-----|---------|-----------------------------------------------------------------|-------|

|   |     | 3.4.2   | Full System Simulation of 2.5D Systems with PNoC                | 41    |

|   |     | 3.4.3   | Liquid Cooling via Microchannels Simulation Results             | 42    |

|   |     | 3.4.4   | Standard-Cell-Level Validation of PACT against COMSOL and HotSp | ot 46 |

|   |     | 3.4.5   | Standard-Cell-Level Comparison of PACT against MTA              | 53    |

|   | 3.5 | Case St | tudy: Modeling Diamond Heat Spreaders Using PACT                | 54    |

|   |     | 3.5.1   | Introduction                                                    | 55    |

|   |     | 3.5.2   | Materials and Methods                                           | 56    |

|   |     | 3.5.3   | Results and Discussions                                         | 60    |

| 4 | Mod | eling E | merging Cooling Methods via Machine Learning                    | 75    |

|   | 4.1 | Introdu | ction                                                           | 75    |

|   | 4.2 | Two-Pl  | nase VCs with Micropillar Wick Evaporators CTM                  | 76    |

|   |     | 4.2.1   | Background on VCs                                               | 76    |

|   |     | 4.2.2   | Compact Modeling Methodology                                    | 77    |

|   |     | 4.2.3   | Dry-out Heat Flux Analytical Model                              | 79    |

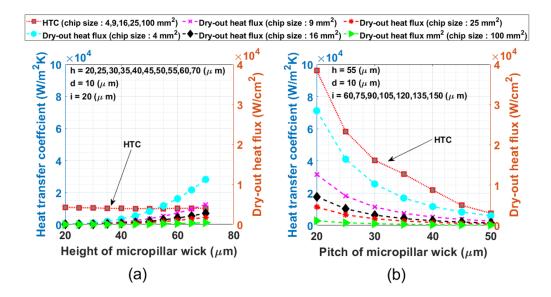

|   |     | 4.2.4   | Parametric Study                                                | 80    |

|   |     | 4.2.5   | Validation of the Proposed Model                                | 81    |

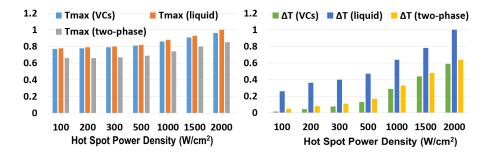

|   |     | 4.2.6   | Cooling Performance Evaluation                                  | 83    |

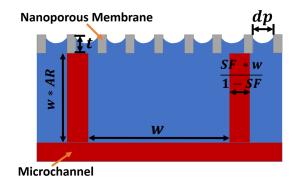

|   | 4.3 | Two-Pl  | nase VCs with Hybrid Wick Evaporators CTM                       | 85    |

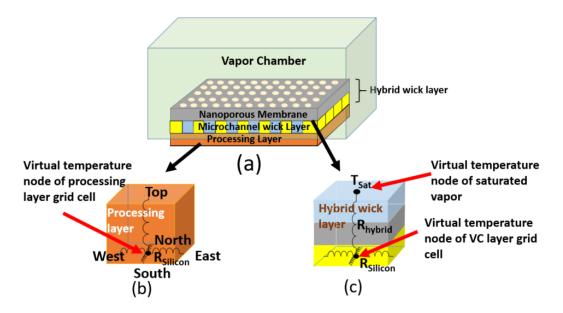

|   |     | 4.3.1   | Compact Modeling Methodology                                    | 85    |

|   |     | 4.3.2   | COMSOL Model                                                    | 87    |

|   | 4.4 | An ML   | -Based Thermal Simulation Framework for Emerging Two-Phase      |       |

|   |     | Cooling | g Technologies                                                  | 88    |

|   |     | 4.4.1   | A Temperature-Dependent HTC Simulation Framework                | 89    |

|   |     | 4.4.2   | An ML-Based Temperature-Dependent HTC Simulation Framework      | 89    |

|   |     | 4.4.3   | Validation of the ML Model                                      | 91    |

|   |     | 4.4.4   | Validation of the ML-Based Temperature-Dependent HTC Simu-    |     |

|---|-----|---------|---------------------------------------------------------------|-----|

|   |     |         | lation Framework                                              | 92  |

|   | 4.5 | Impro   | ved ML-Based Simulation Framework for Two-Phase VCs           | 94  |

|   |     | 4.5.1   | Improved Compact Modeling of the Two-Phase VCs                | 95  |

|   |     | 4.5.2   | Improved ML-Based Temperature-Dependent HTC Simulation Frame- | -   |

|   |     |         | work                                                          | 98  |

|   |     | 4.5.3   | Cooling Performance Evaluation of Two-Phase VCs on Realistic  |     |

|   |     |         | Mobile System                                                 | 99  |

|   | 4.6 | Predic  | ting Thermal Profiles via ML                                  | 100 |

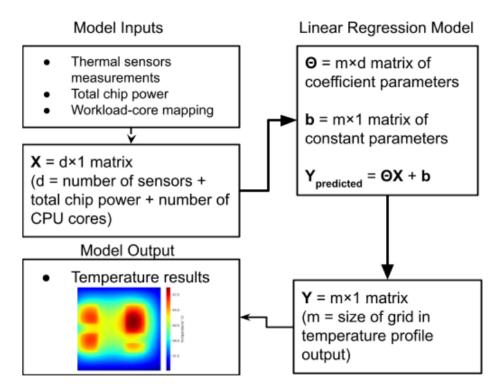

|   |     | 4.6.1   | Methodology                                                   | 102 |

|   |     | 4.6.2   | Results and Discussions                                       | 106 |

| 5 | Opt | imizing | Emerging Cooling Methods for High-Performance Processors via  |     |

|   | Dee | p Learn | <b>iing</b>                                                   | 116 |

|   | 5.1 | Introd  | uction                                                        | 116 |

|   | 5.2 | Two-P   | Phase VCs Optimization Flows                                  | 117 |

|   |     | 5.2.1   | Two-Phase VCs with Micropillar Wick Evaporators Optimization  |     |

|   |     |         | via Grid Search                                               | 117 |

|   |     | 5.2.2   | Two-Phase VCs with Hybrid Wick Evaporators Optimization via   |     |

|   |     |         | MSA                                                           | 118 |

|   | 5.3 | Emerg   | ging Cooling Methods Optimization via CMA-ES                  | 120 |

|   | 5.4 | Emerg   | ging Cooling Methods Optimization via DL                      | 125 |

|   |     | 5.4.1   | Overall CNN Optimization Architecture                         | 127 |

|   |     | 5.4.2   | Training Data Preparation                                     | 128 |

|   |     | 5.4.3   | Hybrid Cooling CNN Architecture                               | 129 |

|   |     |         |                                                               |     |

|   |     | 5.4.4   | Two-Phase VCs with Hybrid Wick Evaporators CNN Architecture . | 131 |

| 6              | Conclusions and Future Work 14 |                                                                     | 140 |

|----------------|--------------------------------|---------------------------------------------------------------------|-----|

|                | 6.1                            | Enabling Fast and Accurate Parallel Thermal Simulations with PACT   | 140 |

|                | 6.2                            | Modeling Emerging Cooling Methods via Machine Learning              | 142 |

|                | 6.3                            | Optimizing Emerging Cooling Methods for High-Performance Processors |     |

|                |                                | via Deep Learning                                                   | 143 |

| References 146 |                                |                                                                     | 146 |

| Cu             | Curriculum Vitae 156           |                                                                     |     |

# **List of Tables**

| 3.1  | Solvers, cooling methods, and inputs of PACT and of existing compact                 |    |

|------|--------------------------------------------------------------------------------------|----|

|      | thermal simulators (e.g., HotSpot (Skadron et al., 2003), 3D-ICE (Sridhar            |    |

|      | et al., 2014), and ThermalScope (Allec et al., 2008)). BE stands for the             |    |

|      | Backward Euler solver, and TRAP is a hybrid solver of the Backward Euler             |    |

|      | and the Trapezoidal method. Full industrial design means that PACT takes             |    |

|      | real-world standard-cell designs as input, such as designs from OpenROAD.            | 20 |

| 3.2  | Information about available solvers in PACT.                                         | 37 |

| 3.3  | Experimental setup of monolithic 3D chip and the SCC-based chip simula-              |    |

|      | tions                                                                                | 41 |

| 3.4  | Simulation results of the monolithic 3D chip and the SCC-based chip                  | 41 |

| 3.5  | Experimental setup of PNoC simulations.                                              | 42 |

| 3.6  | PNoC simulation results.                                                             | 44 |

| 3.7  | Validation setup of liquid cooling via microchannels simulations                     | 46 |

| 3.8  | Validation setup of HotSpot, COMSOL, and PACT.                                       | 48 |

| 3.9  | Statistics of the realistic MPSoCs from the OpenROAD benchmark set                   | 49 |

| 3.10 | Intel i7 6950 $\times$ steady-state results. ID stands for chip stack identification |    |

|      | number. $T_{max}$ stands for maximum temperature (°C) and $\Delta T$ stands for      |    |

|      | temperature gradient (° $C$ ).                                                       | 65 |

| 3.11 | IBM Power9 steady-state results. ID stands for chip stack identification             |    |

|      | number. $T_{max}$ stands for maximum temperature (°C) and $\Delta T$ stands for      |    |

|      | temperature gradient (°C)                                                            | 65 |

| 3.12 | PicoSoC steady-state results. ID stands for chip stack identification num-           |

|------|--------------------------------------------------------------------------------------|

|      | ber. $T_{max}$ stands for maximum temperature (°C) and $\Delta T$ stands for temper- |

|      | ature gradient (°C)                                                                  |

| 3.13 | Liquid cooling via microchannels material properties                                 |

| 4.1  | Coolant and micropillar parameters                                                   |

| 4.2  | Comparison between proposed CTM and COMSOL                                           |

| 4.3  | Structural properties and simulation parameters                                      |

| 4.4  | Optimal geometries (h, d, i) of two-phase VCs and estimated pumping                  |

|      | power of liquid cooling via microchannels and microchannel-based two-                |

|      | phase cooling (G = 560 $kg/m^2s$ )                                                   |

| 4.5  | Hybrid wick geometry parameters and valid range                                      |

| 4.6  | Worst-case results from the k-fold CV tests. MAE stands for mean absolute            |

|      | error, RMSE stands for root mean square error. The errors are normalized             |

|      | with respect to the golden HTC data                                                  |

| 4.7  | Hybrid wick geometries for validation tests                                          |

| 4.8  | Naming conventions of the parameters                                                 |

| 4.9  | 5-fold CV results                                                                    |

| 5.1  | Details parameters for hybrid cooling CNN alternatives                               |

| 5.2  | Accuracy results for different hybrid cooling CNN regression alternatives 131        |

| 5.3  | Accuracy results for different activation functions. Accuracy and R2 score           |

|      | are averaged for liquid flow velocity and current                                    |

| 5.4  | Detailed parameters for two-phase VCs with hybrid wick evaporators CNN               |

|      | alternatives                                                                         |

| 5.5  | Accuracy results for different two-phase VCs with hybrid wick evaporators            |

|      | CNN regression alternatives                                                          |

| 5.6  | Validation results of the proposed CNN architectures                                 |

xvi

| 5.7 | Predicted parameters using our proposed CNN architectures and baseline |

|-----|------------------------------------------------------------------------|

|     | parameters generated using the baseline methods for PicoSoC            |

| 5.8 | IBM Power9 processor power breakdown                                   |

| 5.9 | IBM Power9 processor optimal cooling parameters, maximum tempera-      |

|     | ture, and cooling power                                                |

# **List of Figures**

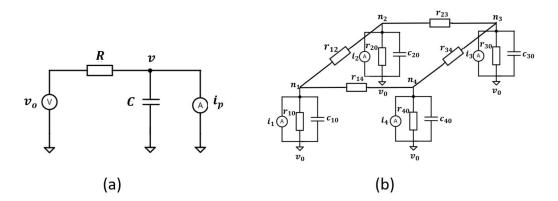

| 2.1 | (a) A simple thermal RC circuit (Pedram and Nazarian, 2006). R is the             |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | thermal resistor, $C$ is the thermal capacitor, $v_0$ is the ambient temperature, |    |

|     | and $v$ is the temperature of the node. (b) An equivalent RC network to           |    |

|     | model temperature distribution (Pedram and Nazarian, 2006)                        | 9  |

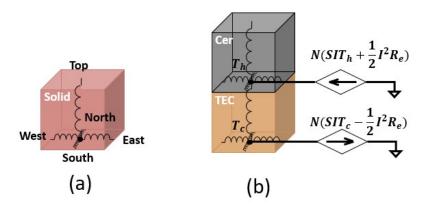

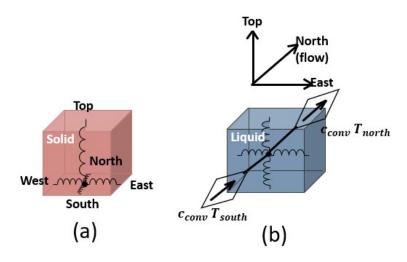

| 2.2 | (a) Default grid cell and (b) TEC grid cell (Kaplan et al., 2017)                 | 12 |

| 2.3 | COMSOL model of the TEC device (Kaplan et al., 2017)                              | 12 |

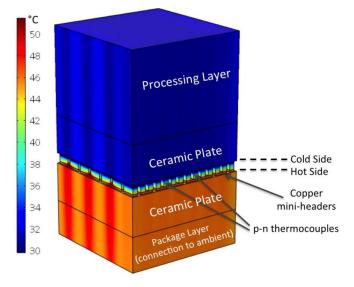

| 2.4 | Liquid cooling via microchannels 3D IC architecture (Sridhar et al., 2014).       | 13 |

| 2.5 | (a) Default grid cell and (b) Liquid grid cell (Sridhar et al., 2013a)            | 14 |

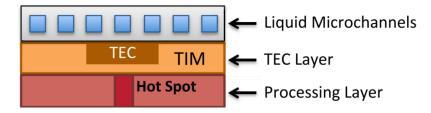

| 2.6 | Front view of a hybrid cooling design (Kaplan et al., 2019)                       | 16 |

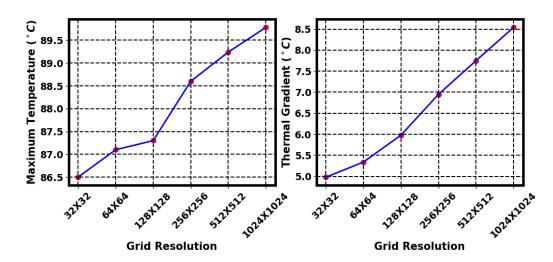

| 3.1 | Temperature profiles for a standard-cell design at various grid resolutions.      |    |

|     | The maximum temperature and thermal gradient plots are expected to sat-           |    |

|     | urate with higher grid resolutions (> $1024 \times 1024$ )                        | 20 |

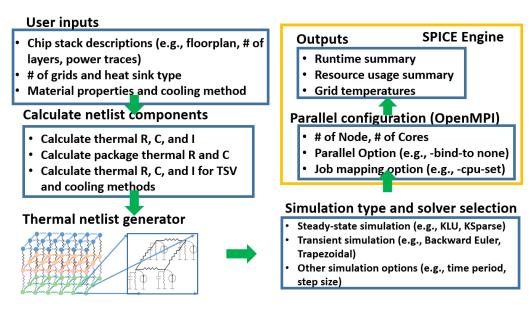

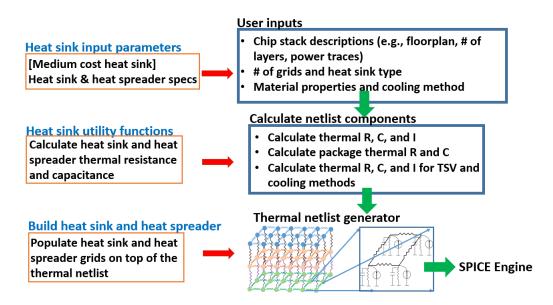

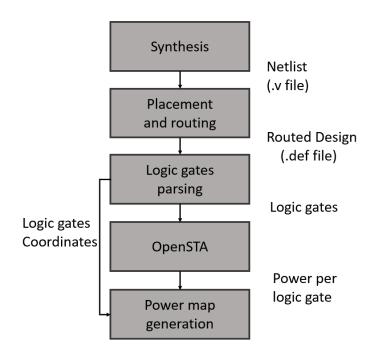

| 3.2 | PACT simulation flow.                                                             | 25 |

| 3.3 | SPICE circuit component usage in PACT                                             | 28 |

| 3.4 | The high-level simulation flow with the medium-cost heat sink                     | 29 |

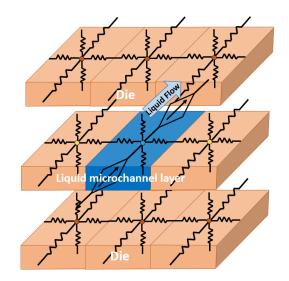

| 3.5 | A small section of a liquid-cooled chip stack.                                    | 31 |

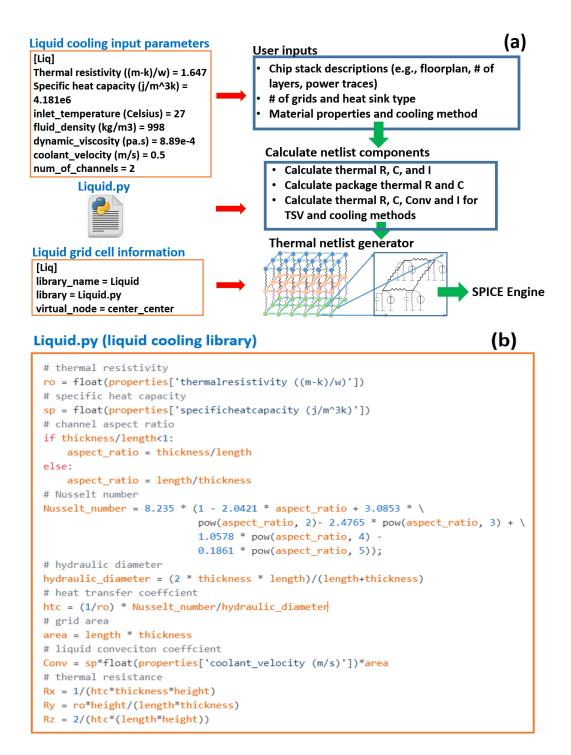

| 3.6 | (a) The high-level simulation flow with liquid cooling via microchannels          |    |

|     | and (b) the additional liquid cooling library file for implementing a CTM         |    |

|     | for liquid cooling via microchannels.                                             | 33 |

| 3.7 | PNoC simulation framework.                                                        | 35 |

| 3.8 | The flow diagram of OpenROAD.                                                     | 36 |

| 3.9  | Transient simulation time of a two-layer chip stack.                    | 37 |

|------|-------------------------------------------------------------------------|----|

| 3.10 | Thermal maps for running application bt with 96 threads and 10% perfor- |    |

|      | mance constraint using original PNoC simulation framework and PNoC      |    |

|      | simulation framework using PACT. MRRG is on the interposer layer. The   |    |

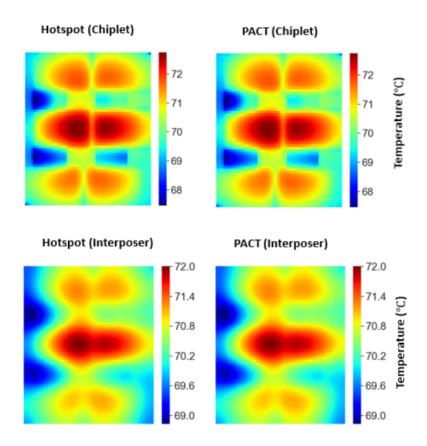

|      | number of grids used in the simulation is set to $64 \times 64$ .       | 43 |

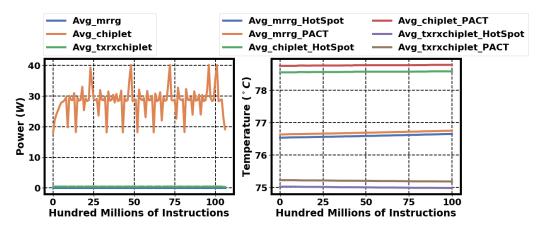

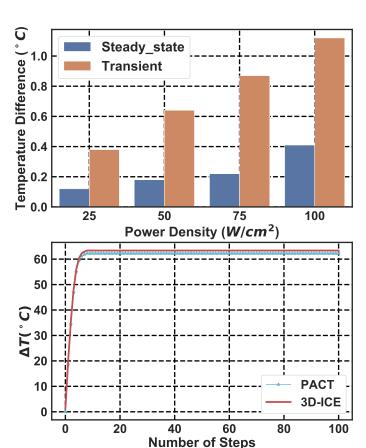

- 3.11 Transient temperature results for running application hpccg with 96 threads and 10% performance constraint using original PNoC simulation framework and PNoC simulation framework using PACT. The number of grids used in the simulation is set to  $64 \times 64$ . The left image shows the average power traces and the right image shows the average temperature traces. . . 44

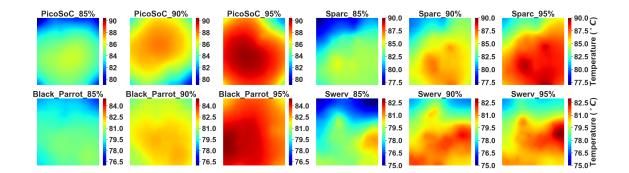

- 3.14 PACT's thermal maps for the MPSoCs from OpenROAD. The number of grids used in the simulation is set to 256×256. Different utilization levels (shown next to chip names) affect floorplan, chip size, and power density.

48

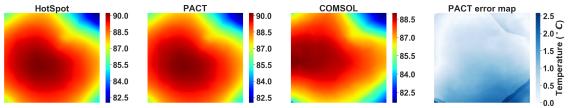

- 3.15 Thermal maps for PicoSoC with 95% utilization simulated using HotSpot,

PACT, and COMSOL. The rightmost image shows the error map of PACT when compared to HotSpot. The number of grids used in the simulation is set to 256×256.

49

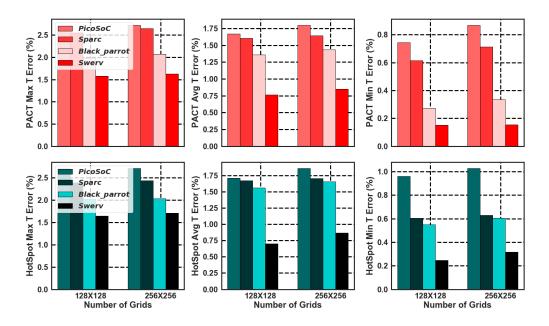

| 3.16                                                                 | Steady-state grid temperature validation results (utilization = 95%). MP-            |                                                                                                                        |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|                                                                      | SoCs with 95% utilization result in the highest maximum, average, and                |                                                                                                                        |

|                                                                      | minimum grid temperature error. The error is calculated with respect to              |                                                                                                                        |

|                                                                      | COMSOL                                                                               | 50                                                                                                                     |

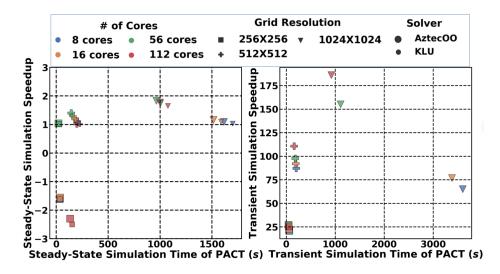

| 3.17                                                                 | Steady-state and transient simulation times of PACT. The speedup of PACT             |                                                                                                                        |

|                                                                      | against HotSpot is shown on the y-axis. The speedup is computed as the               |                                                                                                                        |

|                                                                      | ratio of the simulation times of HotSpot and PACT. Negative values mean              |                                                                                                                        |

|                                                                      | HotSpot is faster than PACT for those cases.                                         | 50                                                                                                                     |

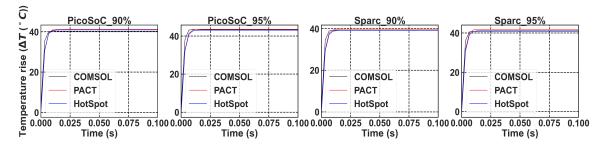

| 3.18                                                                 | Transient validation results. The number of grids used in the simulation is          |                                                                                                                        |

|                                                                      | set to $256 \times 256$ . Due to the space limit, we only show the results that have |                                                                                                                        |

|                                                                      | the highest transient temperature difference                                         | 51                                                                                                                     |

| 3.19                                                                 | Synthetic power traces for PACT and HotSpot simulations. Due to the                  |                                                                                                                        |

|                                                                      | space limit, we only show the results that have the highest temperature              |                                                                                                                        |

|                                                                      |                                                                                      |                                                                                                                        |

|                                                                      | difference                                                                           | 52                                                                                                                     |

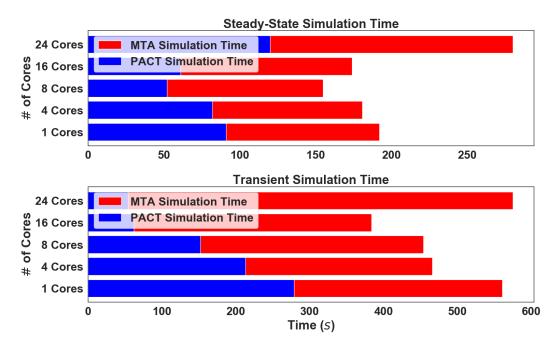

| 3.20                                                                 | difference.Steady-state and transient simulation time of PACT and MTA.               |                                                                                                                        |

|                                                                      |                                                                                      | 54                                                                                                                     |

| 3.21                                                                 | Steady-state and transient simulation time of PACT and MTA                           | 54<br>57                                                                                                               |

| 3·21<br>3·22                                                         | Steady-state and transient simulation time of PACT and MTA                           | 54<br>57<br>58                                                                                                         |

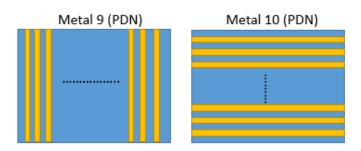

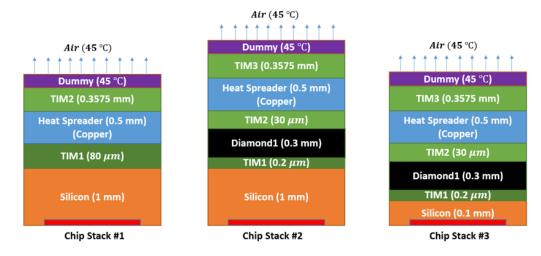

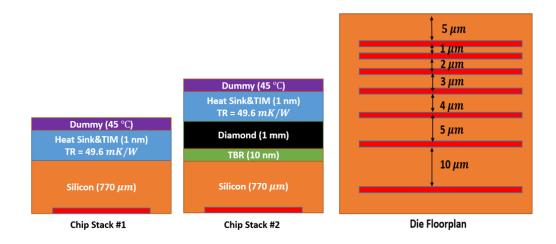

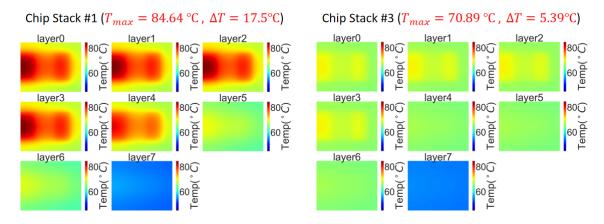

| 3·21<br>3·22<br>3·23                                                 | Steady-state and transient simulation time of PACT and MTA                           | 54<br>57<br>58                                                                                                         |

| 3·21<br>3·22<br>3·23<br>3·24                                         | Steady-state and transient simulation time of PACT and MTA                           | 54<br>57<br>58<br>58                                                                                                   |

| 3.21<br>3.22<br>3.23<br>3.24<br>3.25                                 | Steady-state and transient simulation time of PACT and MTA                           | 54<br>57<br>58<br>58<br>59                                                                                             |

| 3.21<br>3.22<br>3.23<br>3.24<br>3.25<br>3.26                         | Steady-state and transient simulation time of PACT and MTA                           | 54<br>57<br>58<br>58<br>59<br>59                                                                                       |

| 3.21<br>3.22<br>3.23<br>3.24<br>3.25<br>3.26<br>3.27                 | Steady-state and transient simulation time of PACT and MTA                           | <ul> <li>54</li> <li>57</li> <li>58</li> <li>58</li> <li>59</li> <li>59</li> <li>61</li> </ul>                         |

| 3.21<br>3.22<br>3.23<br>3.24<br>3.25<br>3.26<br>3.27<br>3.28         | Steady-state and transient simulation time of PACT and MTA                           | <ul> <li>54</li> <li>57</li> <li>58</li> <li>58</li> <li>59</li> <li>59</li> <li>61</li> <li>62</li> </ul>             |

| 3.21<br>3.22<br>3.23<br>3.24<br>3.25<br>3.26<br>3.27<br>3.28<br>3.29 | Steady-state and transient simulation time of PACT and MTA.                          | <ul> <li>54</li> <li>57</li> <li>58</li> <li>58</li> <li>59</li> <li>59</li> <li>61</li> <li>62</li> <li>66</li> </ul> |

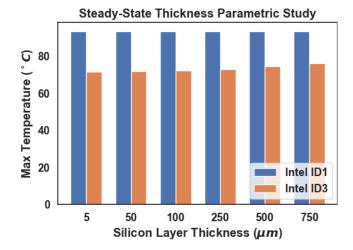

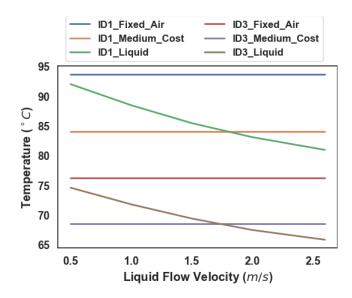

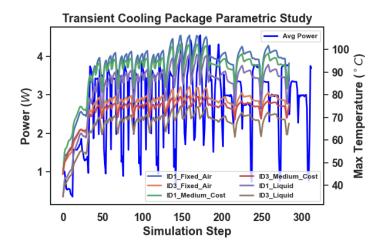

| Steady-state silicon layer thickness parametric study results for Intel i7         |                                                                                                                            |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 6950×                                                                              | 70                                                                                                                         |

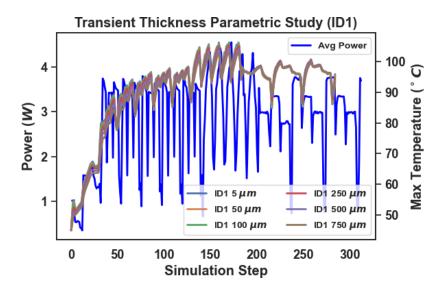

| Intel i7 $6950 \times$ chip stack 1 silicon layer thickness transient parametric   |                                                                                                                            |

| study results.                                                                     | 70                                                                                                                         |

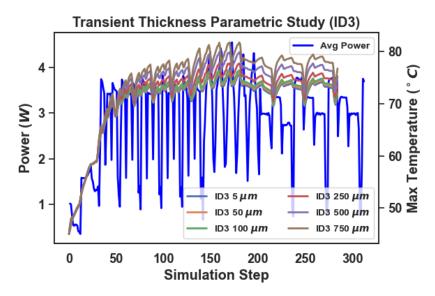

| Intel i7 $6950 \times$ chip stack 3 silicon layer thickness transient parametric   |                                                                                                                            |

| study results.                                                                     | 71                                                                                                                         |

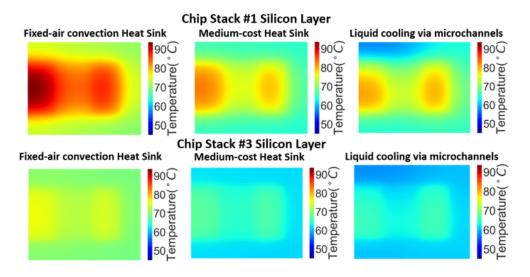

| Steady-state heat maps for parametric study of cooling packages. Liquid            |                                                                                                                            |

| flow velocity is set to 2.6 $m/s$                                                  | 72                                                                                                                         |

| Intel i7 6950 $\times$ silicon layer steady-state cooling package parametric study |                                                                                                                            |

| results (maximum temperature).                                                     | 73                                                                                                                         |

| Intel i7 $6950 \times$ silicon layer transient cooling package parametric study    |                                                                                                                            |

| results                                                                            | 74                                                                                                                         |

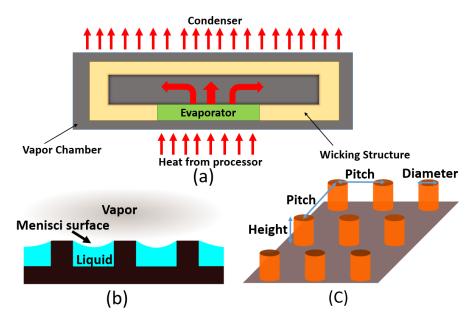

| (a) VC structure view. (b) micropillar wick side view, and (c) micropillar         |                                                                                                                            |

|                                                                                    | 77                                                                                                                         |

|                                                                                    |                                                                                                                            |

|                                                                                    | 78                                                                                                                         |

|                                                                                    |                                                                                                                            |

|                                                                                    | 82                                                                                                                         |

|                                                                                    |                                                                                                                            |

|                                                                                    | -                                                                                                                          |

|                                                                                    |                                                                                                                            |

|                                                                                    |                                                                                                                            |

|                                                                                    | 84                                                                                                                         |

| A hybrid wick evaporator cross-section view.                                       | 85                                                                                                                         |

|                                                                                    | $6950 \times \dots $ |

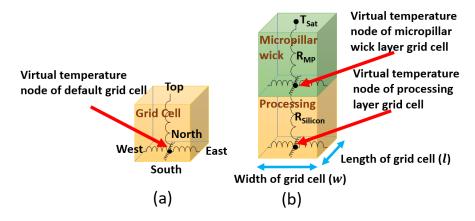

| 4.6  | (a) The chip stack of the processing layer and two-phase VCs with hybrid                |

|------|-----------------------------------------------------------------------------------------|

|      | wick evaporators, (b) processing layer grid cell, and (c) hybrid wick layer             |

|      | grid cell                                                                               |

| 4.7  | Temperature-dependent HTC simulation framework and our proposed ML-                     |

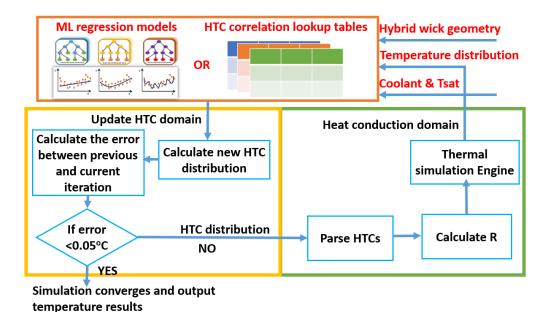

|      | based temperature-dependent HTC simulation framework 90                                 |

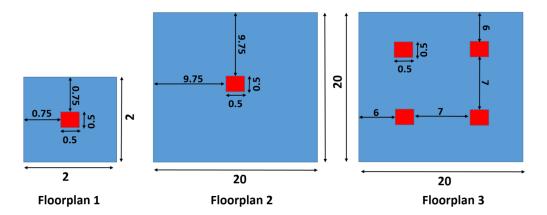

| 4.8  | Floorplans used in validation. Dimensions are in <i>mm</i>                              |

| 4.9  | Non-uniform power profile maximum and average temperature error vali-                   |

|      | dation results. $PD_{Hs}$ stands for hot spot power density                             |

| 4.10 | (a) The chip stack of the processing layer and two-phase VCs with hybrid wick           |

|      | evaporators, (b) processing layer grid cell, (c) hybrid wick layer grid cell, (d) vapor |

|      | core grid cell, and (e) condenser grid cell                                             |

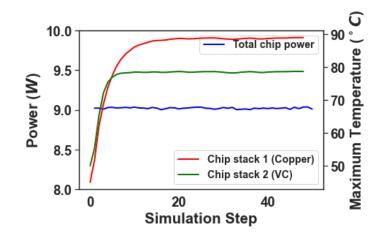

| 4.11 | Improved ML-based temperature-dependent simulation framework 99                         |

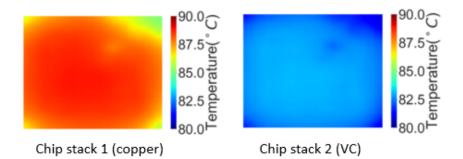

| 4.12 | Steady-state heat maps                                                                  |

| 4.13 | Transient comparison results                                                            |

| 4.14 | Diagram of the ML model                                                                 |

| 4.15 | Original total chip power from McPAT, split by the number of enabled                    |

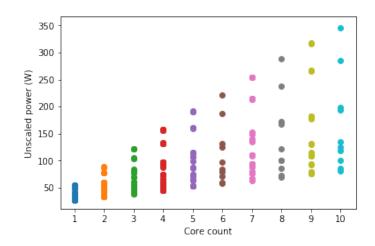

|      | cores                                                                                   |

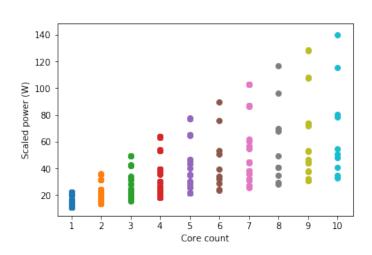

| 4.16 | Scaled total chip power, split by the number of enabled cores                           |

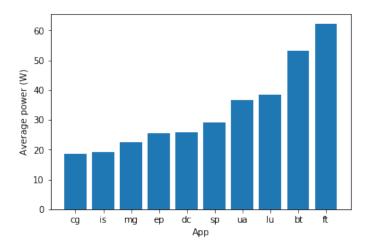

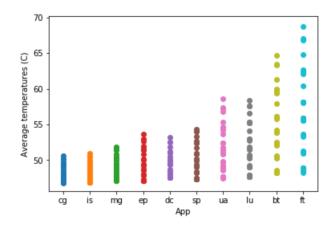

| 4.17 | Average power of each application in the NAS parallel benchmarks 108                    |

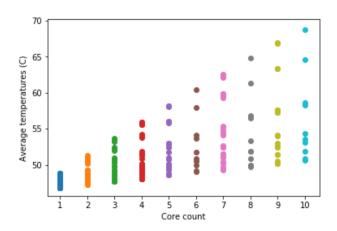

| 4.18 | Average temperatures for applications (° <i>C</i> ), split by the number of enabled     |

|      | cores used                                                                              |

| 4.19 | Average temperatures (° <i>C</i> ) for the number of enabled cores to run the ap-       |

|      | plications, split by application and sorted in ascending order by average               |

|      | power                                                                                   |

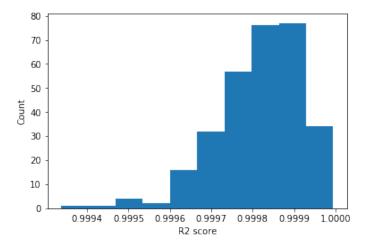

| 4.20 | Histogram of R2 score distribution across 300 different thermal sensor                  |

|      | placements used as input to the model                                                   |

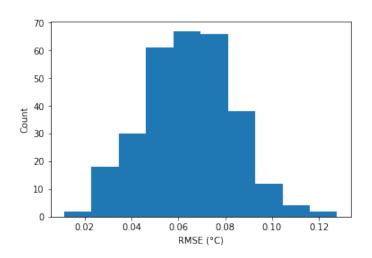

| 4.21 | Histogram of RMSE distribution across 300 different thermal sensor place-        |

|------|----------------------------------------------------------------------------------|

|      | ments used as input to the model                                                 |

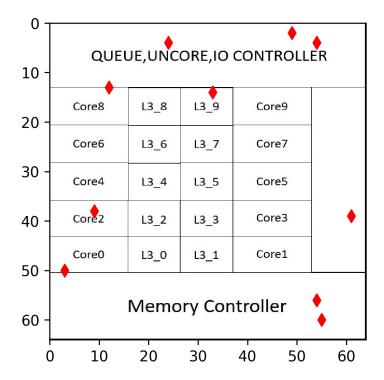

| 4.22 | Selected thermal sensor placement for our experiments. Red markers indi-         |

|      | cate thermal sensors                                                             |

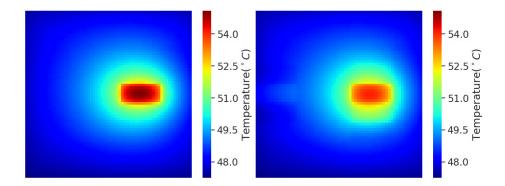

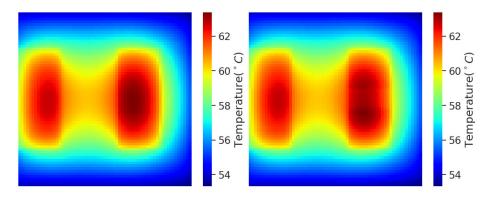

| 4.23 | Heat map comparison for the worst case. The left heat map is the golden          |

|      | heat map, and the right heat map is the predicted heat map                       |

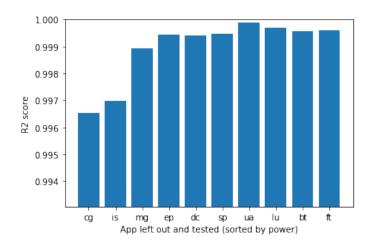

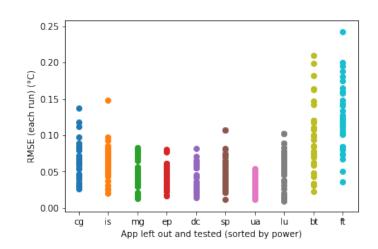

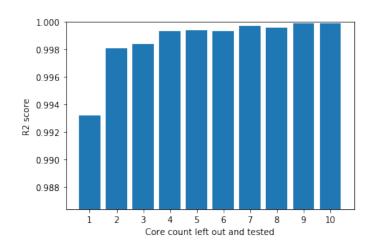

| 4.24 | Average LOOCV R2 scores on applications                                          |

| 4.25 | LOOCV RMSEs on applications                                                      |

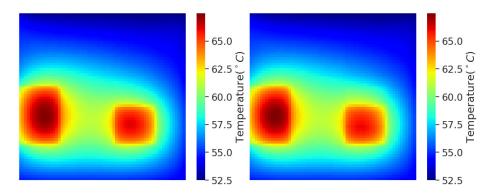

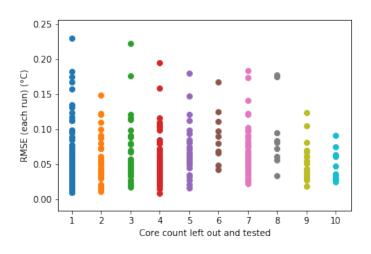

| 4.26 | Heat map comparisons for the worst case when the number of cores used            |

|      | is equal to 5. The left heat map is the golden heat map, and the right heat      |

|      | map is the predicted heat map                                                    |

| 4.27 | Average LOOCV R2 scores on enabled cores                                         |

| 4.28 | LOOCV RMSEs on enabled cores                                                     |

| 4.29 | Heat map comparison for the worst case when the number of enabled cores          |

|      | is equal to 10. The left heat map is the golden heat map, and the right heat     |

|      | map is the predicted heat map                                                    |

| 5.1  | Experimental floorplans. Dimensions are in mm                                    |

| 5.2  | Proposed optimization flow                                                       |

| 5.3  | Synthetic chip floorplans                                                        |

| 5.4  | Results for on-chip temperature constraint = $65^{\circ}C$ . The format for two- |

|      | phase VCs with hybrid wick evaporator is {coolant, hot spot temperature,         |

|      | cooling power}. The format for hybrid cooling is {liquid flow velocity,          |

|      | TEC current, hot spot temperature, cooling power}                                |

| 5.5  | DL-based cooling optimization flow                                               |

| 5.6  | Optimal hybrid cooling CNN architecture                                          |

| 5.7  | CNN architectures accuracy results                                               |

# **List of Abbreviations**

| 2RM    | 2-resistor model                                      |

|--------|-------------------------------------------------------|

| 4RM    | 4-resistor model                                      |

| BE     | Backward Euler                                        |

| CFD    | Computational Fluid Dynamics                          |

| CMA-ES | Covariance matrix adaptation evolution strategy       |

| CNN    | Convolutional Neural Network                          |

| СОР    | Coefficient of performance                            |

| СТМ    | Compact thermal model                                 |

| CV     | Cross-validation                                      |

| DEF    | Design exchange format                                |

| DL     | Deep Learning                                         |

| DSMC   | Direct Simulation Monte Carlo                         |

| FEM    | Finite element method                                 |

| GDR    | Gradient boosting regression                          |

| GDS    | Graphic data stream                                   |

| НТС    | Heat transfer coefficient                             |

| IC     | Integrated circuit                                    |

| ID     | Chip stack identification number                      |

| ISA    | Instruction set architecture                          |

| LOOCV  | Leave one out cross-validation                        |

| MAE    | Mean absolute error                                   |

| MGHPCC | Massachusetts Green High-Performance Computing Center |

| MIV    | Monolithic inter-tier vias                            |

| ML     | Machine Learning                                      |

| MPSoC  | Multiprocessor system-on-chips                        |

| MRRG   | Microring Resonator Group                             |

| MRR    | Microring Resonator                                   |

| MSA    | Multi-start simulated annealing                       |

| MSE    | Mean square error                                     |

| MTA    | Manchester Thermal Analyzer                           |

| NNR    | Neural network regression                             |

| PACT   | A parallel compact thermal simulator                  |

| PNoC   | Photonic network-on-chip                              |

| PWL    | Piece-wise linear                                     |

| RK4    | 4 <sup>th</sup> order Runge-Kutta                     |

|        |                                                       |

| RMSE  | Root mean square error                              |

|-------|-----------------------------------------------------|

| RTL   | Register-transfer level                             |

| SPICE | Simulation Program with Integrated Circuit Emphasis |

| SVR   | Support vector regression                           |

| TDP   | Thermal design power                                |

| TEC   | Thermoelectric cooler                               |

| TIM   | Thermal interface material                          |

| TSV   | Through-silicon vias                                |

| VC    | Vapor chamber                                       |

# Chapter 1 Introduction

#### **1.1 Motivation and Key Contributions**

Over the last few decades, on-chip power densities have grown tremendously following the down-scaling of transistors. Power densities that reach  $1-2 \ KW/cm^2$  caused by the performance boost of scaling already occur in high-performance chips and result in amplified localized hot spots (Schultz et al., 2016). These on-chip hot spots not only degrade the performance of the chip but also generate larger sub-threshold leakage power and create reliability challenges (Schultz et al., 2016; Saini and Mehra, 2012).

Conventional on-chip cooling solutions such as forced air cooling via fans or pin-fin heat sinks are often insufficient to mitigate high-power-density hot spots and result in over/under-cooling. Emerging cooling technologies such as liquid cooling via microchannels (Dang et al., 2010), thermoelectric coolers (TECs) (Chowdhury et al., 2009), two-phase vapor chambers (VCs) (Bulut et al., 2019), and hybrid cooling options (Yazawa et al., 2012) (e.g., of liquid cooling via microchannels and TECs) have the potential to provide better cooling performance compared to the conventional cooling solutions. However, there is no obvious winner in terms of cooling efficiency among all these emerging cooling technologies. These potential solutions' cooling performance and cooling power vary significantly based on the cooling parameters (such as liquid flow velocity, evaporator design, TEC current, etc.) (Yuan et al., 2020; Yuan et al., 2019a; Yuan et al., 2019b). The cooling technologies and the cooling parameters also need to consider the chip architecture, chip size, floorplan, and the power profiles of the applications running on the given chip.

To minimize the cooling power while satisfying chip thermal constraints, there is a need for an optimization flow that enables rapid and accurate selection of the optimal cooling solution and the associated cooling parameters for a given chip and application profile.

A key enabler to such a cooling design optimization flow is a set of accurate and fast models for various cooling technologies. A common approach towards this direction is using compact thermal models (CTMs) that model heat dissipation with an equivalent lumped circuit model (Pedram and Nazarian, 2006). However, existing thermal simulation tools are limited by several major challenges that prevent them from providing fast solutions to large problem sizes, which are necessary to conduct standard-cell-level thermal analysis or to evaluate new technologies or large chips. In addition, some specific cooling methods, such as two-phase cooling methods, require additional Computational Fluid Dynamics (CFD) simulations. CFD simulations are often time-consuming and have large memory requirements (e.g., simulating a *mm*-scale chip model can take from hours to multiple days and easily requires tens of GBs of memory). Given the vast solution space of possible cooling solutions (including possible hybrids) and cooling parameters, the optimal solution search time is still prohibitively time-consuming with CTMs (Yuan et al., 2019a). In addition to cooling design choice possibilities, the optimization flow also needs to consider the specific chip design and power profile changes. In this case, using a simple grid search to find the optimal cooling design for even a small-sized chip floorplan and its typical power profile could easily take up to days (Yuan et al., 2019a).

This thesis claims that combining a compact thermal modeling methodology with machine learning (ML) models enables rapidly and accurately predicting the optimal cooling solution and its cooling parameters for arbitrary chip designs.

The thesis aims to realize this optimization flow through three fronts:

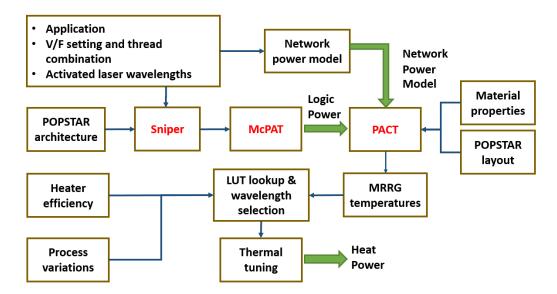

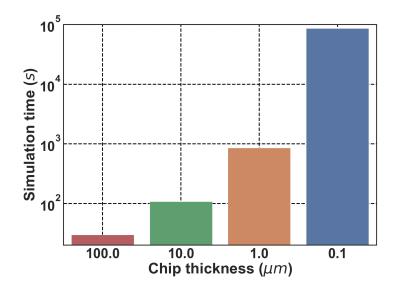

• Enabling fast and accurate parallel thermal simulations with PACT: We pro-

pose a parallel compact thermal simulator, PACT<sup>1</sup>, that enables speedy and accurate standard-cell-level to architecture-level thermal analysis for processors. PACT has the following features: (i) it utilizes the parallelism in modern computing systems to conduct parallel thermal simulations to speed up the process of solving problems with a large number of grid nodes (e.g., for standard-cell-level problems or modeling the ultra-thin layers in a monolithic 3D stack), (ii) it offers support for various steady-state and transient solvers to speed up simulation time while maintaining the desired accuracy level, and (iii) it can be easily extended to support emerging integration and cooling technologies by modifying the thermal netlist. We interface PACT with OpenROAD (Ajayi et al., 2019), an end-to-end silicon compiler to allow the evaluation of thermal behaviors of full standard-cell-level industry designs directly. We validate PACT's accuracy by comparing it to COMSOL, using full standard-celllevel industrial designs provided by OpenROAD. Compared to COMSOL, PACT has a maximum temperature error of 2.77% for steady-state and 3.28% for transient simulation. To demonstrate the applicability of PACT, we run standard-cell-level to architecture-level thermal simulations with realistic 2D and monolithic 3D integrated circuits (ICs) using PACT and a well-known compact thermal simulator, HotSpot (Skadron et al., 2003). Compared to HotSpot, PACT reduces the steady-state simulation time from more than 3 hours to only 16 minutes for simulating a monolithic 3D IC. PACT also speeds up the transient simulation time of a 256-core 2D IC from more than three days to less than 19 minutes. When simulating the full standard-celllevel industrial designs from OpenROAD, PACT shows up to  $232 \times$  speedup with the same accuracy level compared to HotSpot. PACT is able to model and evaluate the thermal behaviors of emerging integration (e.g., monolithic 3D) and cooling technologies (e.g., two-phase vapor chambers). Because of the fast simulation speed and the high extensibility, PACT enables the co-design of the computing system and

<sup>&</sup>lt;sup>1</sup>PACT is open-sourced at https://github.com/peaclab.

cooling system to achieve better energy efficiency or higher computing performance improvements under the temperature constraints (see Chapter 3 for further details).

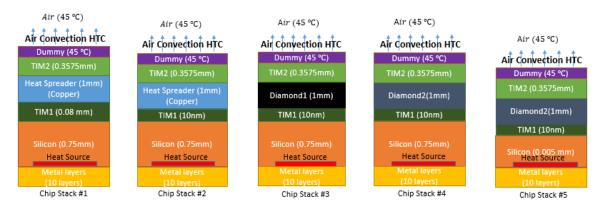

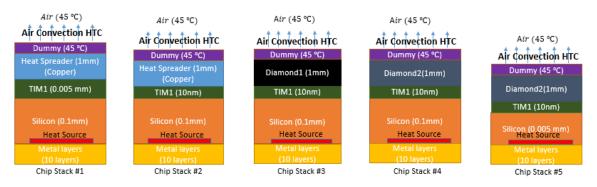

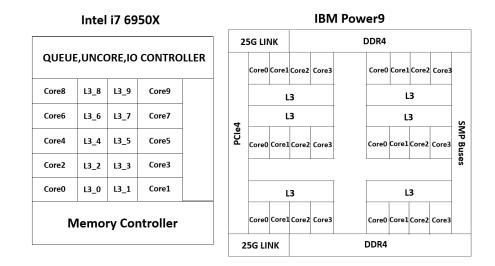

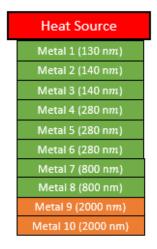

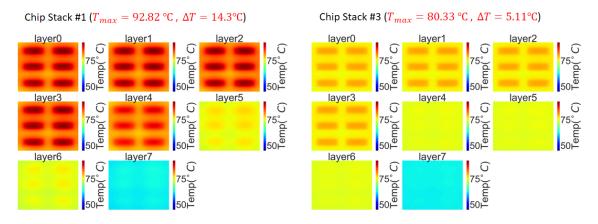

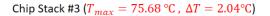

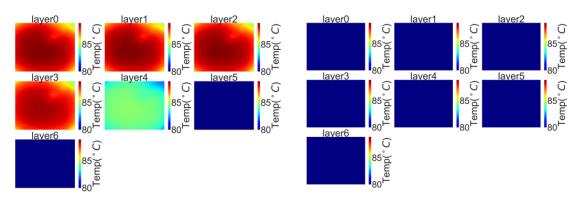

To further demonstrate the extensibility and applicability of PACT, we model *labgrown diamond heat spreaders* in PACT and conduct steady-state and transient thermal simulations with various high-performance chips to evaluate the cooling performance of lab-grown diamond heat spreaders. We run benchmark applications on real-world-like high-performance chips using popular architecture-level performance and power simulators to obtain transient power traces. The generated transient power traces are used as inputs to PACT to perform transient thermal analysis with lab-grown diamond heat spreaders and traditional copper heat spreaders. For each high-performance chip under test, we evaluate the thermal maps, maximum temperature reductions, and thermal gradient reductions with diamond heat spreaders versus traditional copper heat spreaders. Simulation results show that lab-grown diamond heat spreaders achieve maximum temperature and thermal gradient reductions of up to 26.73°C and 13.75°C when compared to traditional copper heat spreaders, respectively (see Chapter 3.5 for further details).

• Modeling emerging cooling methods via machine learning: We introduce MLenabled modeling methodologies for emerging cooling technologies. Two-phase cooling with VCs is a prevalent cooling method for computing systems with tight power and thermal budget (e.g., mobile systems) as it removes heat effectively and requires minimum additional cooling power (Bulut et al., 2019). Developing fast and accurate two-phase VCs thermal models facilitates early-stage design space exploration and co-optimization for the computing system and this cooling technology. In this thesis, we propose a steady-state CTM for two-phase VCs with micropillar wick evaporators and use the CTM to compare the cooling performance (i.e., hot spot temperature reductions and thermal gradients) against liquid cooling via microchannels and microchannel-based two-phase cooling (see Chapter 4.2 for further details). We also propose a generalized ML-based temperature-dependent heat transfer coefficient (HTC) simulation framework for two-phase cooling solutions. To demonstrate the simulation speedup and accuracy of our proposed simulation framework, we build a CTM for two-phase VCs with hybrid wick evaporators (of nanoporous membrane and microchannels) and integrate it into our proposed simulation framework. Our proposed ML-based simulation framework achieves a  $21 \times$  speedup compared to the COMSOL with an average error of  $0.98^{\circ}C$  (see Chapters 4.3 and 4.4 for further details). We further extend the ML-based thermal simulation framework with the support of transient simulation and vapor core modeling (see Chapter 4.5 for further details). To mitigate the on-chip thermal sensors inaccuracies, we propose an ML and simulation-based temperature profile prediction methodology to predict the heat map based on the measurements from the on-chip digital thermal sensors. Experimental results when running a set of realistic benchmark applications show that our proposed ML and simulation-based temperature profile prediction approach accurately predicts temperatures within an error of less than  $0.25^{\circ}C$  (see Chapter 4.6 for further details).

• Optimizing emerging cooling methods for high-performance processors via deep learning: Researchers have developed fast models for various emerging cooling methods (Kaplan et al., 2014; Kaplan and Coskun, 2015; Kaplan et al., 2017; Kaplan et al., 2019; Sridhar et al., 2013a; Sridhar et al., 2010; Sridhar et al., 2013b; Vaartstra et al., 2019). To select and optimize a cooling solution for a given chip and power profile, there is a need for a fast and accurate optimization flow that selects the most power-efficient cooling solution and its cooling parameters for a given target chip and power profile, such that the cooling power is minimized and the chip temperature stays below a safe threshold. To design such a cooling optimization flow, we

perform two main steps. First, we propose the cooling parameters optimization flow to optimize the cooling performance of two-phase VCs with micropillar wick and hybrid wick evaporators. We demonstrate the accuracy and speedup of this cooling parameters optimization flow against the exhaustive search approach. The proposed two-phase VCs optimization flow is capable of finding better (or similar) cooling parameters than the exhaustive search approach with an average speedup of  $4.37 \times$  (see Chapter 5.2 for further details). Second, we design the target cooling optimization flow that selects the most power-efficient cooling solution and its cooling parameters for a given target chip and power profile (see Chapter 5.3 for further details). However, the optimization time of this cooling optimization flow still takes up to days depending on the granularity of the cooling parameters solution space. To further speed up the optimization time, we propose a systematic way to train novel deep learning (DL) models to predict the optimal cooling methods and cooling parameters for a given chip design at design time. A DL regression model learns the intrinsic information among the chip designs and the cooling solutions, and then generates the optimal cooling solution and the cooling parameters, given a specific chip floorplan and power profile. We have designed multi-output convolutional neural networks (CNNs) to estimate the best cooling method and its cooling design and technology parameters. The cost function used to evaluate the output of the CNN is a function of cooling power, hot spot temperatures, and temperature constraint of the chip. Our results confirm that, when compared to existing optimization methods with the same cost function, our proposed CNN architectures and DL-based optimization flow successfully predict the optimal cooling solution and cooling parameters with a maximum error of less than 4% and a maximum speedup of  $140 \times$  (see Chapter 5.4 for further details).

#### **1.2** Dissertation Organization

The rest of the thesis begins with a discussion on the background and related work of the compact thermal modeling methodology, emerging cooling methods and their CTMs, and optimization of emerging cooling methods for high-performance processors. In Chapter 3, we introduce PACT, a fast and accurate parallel compact thermal simulator that has high applicability and extensibility. We evaluate PACT's accuracy and speed against existing compact thermal simulators and present a case study on modeling lab-grown diamond heat spreaders to demonstrate PACT's applicability and extensibility. Chapter 4 shows the detail of utilizing the compact thermal modeling methodology with ML models to build a fast and accurate two-phase cooling simulation framework. We also discuss the ML and simulation-based temperature profile prediction methodology in Chapter 4. In Chapter 5, we discuss the optimization methods for the emerging cooling models we build in Chapter 4 and provide the DL-based optimization flow that is used to search for the optimal cooling method and its cooling parameters given a chip design and power profile.

## Chapter 2

## **Background and Related Work**

This thesis proposes thermal modeling and optimization of emerging cooling methods using ML models to speed up the thermal simulation time and cooling methods optimization time. In this chapter, we first briefly elaborate on the fundamental of compact thermal modeling methodology. We continue to discuss popular emerging cooling methods for processors and their corresponding CTMs. Finally, we discuss the potential optimization angle to speed up optimization for the optimal cooling solution and its parameters for a given chip design.

### 2.1 Compact Thermal Modeling Methodology

Compact thermal modeling has been designed to overcome the thermal simulation challenges of long simulation times and large memory requirements. A compact model leverages the duality between electrical and thermal properties to model temperature (Pedram and Nazarian, 2006).

The heat diffusion equation is generally used to describe the heat conduction and calculate the temperature distribution of a chip. For homogeneous materials, the corresponding heat equation is shown as follows:

$$\rho c_p \frac{\partial u}{\partial t} = k \left( \frac{\partial^2 u}{\partial x^2} + \frac{\partial^2 u}{\partial y^2} + \frac{\partial^2 u}{\partial z^2} \right) + q.$$

(2.1)

In Equation (2.1), k is the thermal conductivity (W/mK),  $\rho$  is the density of the material  $(kg/m^3)$ ,  $c_p$  is the specific heat (J/kgK), q is the power density  $(W/cm^2)$ , and u is the

temperature (°*C*) of the location (*x*, *y*, *z*) at time *t*. There is a well-known duality between heat flow and electric current. The heat flow (*W*) passing through a thermal resistor (°*C*/*W*) is represented as the electric current (*A*) flowing through an electrical resistance ( $\Omega$ ). The corresponding temperature difference (°*C*) is equivalent to the voltage drop (*V*). In addition, there is also a thermal capacitance (*J*/°*C*) that describes how much heat is absorbed, which is represented as the electric capacitance (*F*). Node temperature is then modeled as the node voltage of an electric RC circuit as shown in Figure 2.1 (a). To model a chip with multiple heat sources, heat conduction from each vertical and horizontal node is modeled as thermal resistance. Node  $n_k$  represents the temperature of the circuit block, and the current source,  $i_k$ , represents the power consumption of the corresponding node.  $v_0$  is the ambient temperature, and  $C_{k0}$  represents the thermal capacitance of the node. A thermal RC network can be built based on the above parameters as shown in Figure 2.1 (b).

**Figure 2**.1: (a) A simple thermal RC circuit (Pedram and Nazarian, 2006). *R* is the thermal resistor, *C* is the thermal capacitor,  $v_0$  is the ambient temperature, and *v* is the temperature of the node. (b) An equivalent RC network to model temperature distribution (Pedram and Nazarian, 2006).

#### 2.2 Emerging Cooling Technologies and CTMs

To overcome the high power density challenges for processor cooling, researchers have developed several emerging cooling solutions targeting various architectures and cooling scenarios: (i) TECs are attractive due to their hot spot mitigation ability; (ii) liquid cooling via microchannels can be used as an inter-layer cooling method to solve the thermalcoupling problems for 3D-stacked chips; and (iii) compared to TEC and liquid cooling via microchannels, hybrid cooling (of liquid cooling via microchannels and TEC) enhances cooling performance while minimizing the cooling power. We next discuss emerging cooling methods and compact thermal modeling methodologies for the aforementioned emerging cooling solutions.

### 2.2.1 TECs

TEC units have gained attraction due to their abilities to remove heat from high power density hot spots effectively (Chowdhury et al., 2009). A TEC unit operates based on the Peltier effect such that when an electric current passes through a TEC unit, heat is absorbed from one side (cold side) and rejected on the other side (hot side) (Chowdhury et al., 2009; Yazawa et al., 2012). TEC units are typically placed directly above hot spots. The amount of heat removed by a TEC unit depends on the Seebeck coefficient (*S*), applied current (*I*), electric resistance ( $\rho_{TEC}$ ), and the temperature difference between the cold side and hot side ( $T_h - T_c$ ). Superlattice-based thin-film TECs made of  $Bi_2Te_3$  have high figure-of-merit (*ZT*) and are directly fabricated on the back of a silicon chip (Sahu et al., 2014; Chowdhury et al., 2009). Existing on-chip TEC devices are composed of ultrathin (5–10  $\mu m$ )  $Bi_2Te_3$ based p-n thermocouples sandwiched between copper mini-headers and are covered with ceramic plates at the outmost surfaces to provide insulation(Chowdhury et al., 2009). The terms that contribute to the heat flow in a TEC unit are shown as follows:

$$Q_c = N(SIT_c - \frac{T_h - T_c}{R_t} - \frac{1}{2}I^2R_e), \qquad (2.2)$$

$$Q_h = N(SIT_h - \frac{T_h - T_c}{R_t} + \frac{1}{2}I^2R_e), \qquad (2.3)$$

where  $SIT_c$  is the Peltier effect term,  $\frac{T_h - T_c}{R_t}$  is the thermal conduction term, and  $\frac{1}{2}I^2R_e$  is the Joule heating term represents by the heat generated by passing a current through the TEC.  $T_c$  and  $T_h$  represent the temperatures of the cold side and the hot side of TEC, respectively.  $R_t$  is the thermal resistance and  $R_e$  is the electrical resistance of a TEC unit (Kaplan et al., 2019).

To model the thermal gradients caused by the Peltier effect, CTMs of TEC typically use a voltage-controlled current source to represent the heat entering and leaving the TEC grid cell (Chowdhury et al., 2009; Yazawa et al., 2012). The chip is divided into grid cells, and the default grid cells are used to represent the processing layer (Figure 2.2 (a)). A typical TEC grid cell is shown in Figure 2.2 (b). In this figure, the bottom surface of the TEC grid cell represents the cold side of the TEC unit, whereas the bottom surface of the ceramic grid cell corresponds to the hot side.

Several prior approaches have created similar CTMs for TECs and analyzed the cooling performance of TECs. For example, a numerical CTM of TEC that includes both thermal and electrical contact resistance predicts the cooling performance of TECs (Chowdhury et al., 2009). Both the temperature measurements from real prototypes and thermal simulation results using TEC CTM show a maximum temperature reduction of  $15^{\circ}C$  owing to the cooling ability of TECs. The thermal resistance of TECs plays a significant role in accurately determining the cooling performance of the TECs (Chowdhury et al., 2009). In addition, TECs' cooling performance is also highly correlated with the value of the bias current.

Recent work has introduced another CTM of TEC to estimate the impact of the bias current on the cooling performance of the TEC units (Kaplan et al., 2017). The TEC device and the chip layers they modeled in COMSOL are illustrated in Figure 2.3. The authors validated the accuracy of their proposed CTM of TEC by comparing the temperature results against the TEC model in COMSOL. The reported max, average, and root mean square

Figure 2.2: (a) Default grid cell and (b) TEC grid cell (Kaplan et al., 2017).

errors (RMSE) of their proposed CTM of TECs against COMSOL are  $3.57^{\circ}C$ ,  $2.07^{\circ}C$ , and  $2.25^{\circ}C$ , respectively. Compared to the COMSOL model, the reported speedup of the CTM of TEC is  $16900 \times$ , while the specific speedup number depends on the number of grids used in CTM simulations and the number of nodes used in COMSOL simulations.

Figure 2.3: COMSOL model of the TEC device (Kaplan et al., 2017).

# 2.2.2 Liquid Cooling via Microchannels

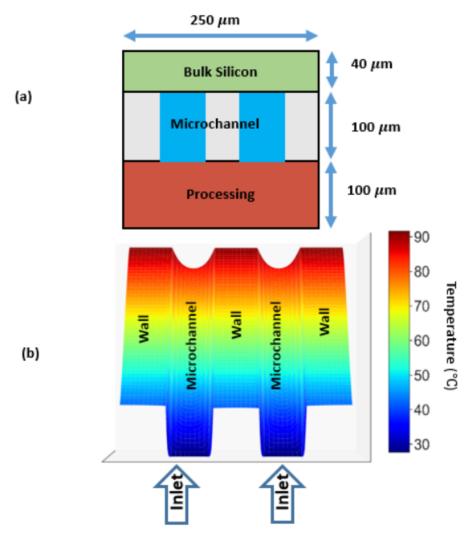

Liquid cooling via microchannels is an attractive cooling solution that uses the liquid convection effect to remove heat from processors (Sridhar et al., 2014; Dang et al., 2010). It is advantageous as an inter-layer cooling method to solve the strong thermal-coupling issues for 3D-stacked architectures (Sridhar et al., 2014). Adding a liquid microchannel layer between processing layers efficiently solves the thermal problems due to the vertical layer stacking. A typical liquid cooling via microchannels 3D IC is shown in Figure 2.4. The coolant that is pumped from the inlet to the outlet absorbs heat due to the convective heat transfer (liquid convection). The chiller outside the system then cools down the heated coolant. There are two main contributors to the convective heat transfer of the coolant: 1) convective heat transfer from the walls of the channel to the liquid and 2) convective heat transfer in the direction of the liquid flow into and out of the current liquid cell.

Figure 2.4: Liquid cooling via microchannels 3D IC architecture (Sridhar et al., 2014).

To build a CTM for liquid cooling via microchannels, one approach (4-resistor model (4RM)) is to use the thermal resistors to represent the convective heat transfer from sidewalls of the microchannels and use a voltage-controlled current source to represent the convective heat transfer along the liquid flow direction (Sridhar et al., 2013a). Figure 2.5 (b) shows the liquid grid cell, and the thermal resistors from sidewalls are defined as follows:

$$R_{top,bottom} = \frac{1}{h_{f,vertical} \cdot w \cdot l},$$

(2.4)

Figure 2.5: (a) Default grid cell and (b) Liquid grid cell (Sridhar et al., 2013a).

$$R_{east,west} = \frac{1}{h_{f,side} \cdot h \cdot l}.$$

(2.5)

In Equations (2.4) and (2.5), h, w, and l stand for the height, width, and length of the grid cell, respectively.  $h_{f,vertical}$  and  $h_{f,side}$  are HTCs for microchannel forced convection.  $h_{f,vertical}$  and  $h_{f,side}$  are obtained from empirical correlations or numerical presimulations. Prior work provides the following formulas to calculate  $h_{f,vertical}$  and  $h_{f,side}$  by assuming imposed axial heat flux and radial isothermal conditions:

$$h_{f,vertical} = h_{f,side} = \frac{k_{coolant} \cdot Nu}{d_h},$$

(2.6)

where  $k_{coolant}$  is the thermal conductivity of the coolant and  $d_h$  is the hydraulic diameters of the channel defined as  $\frac{2hw}{h+w}$ . Nu is the Nusselt number as a function of channel aspect ratio (Sridhar et al., 2013a).  $h_{f,vertical}$ ,  $h_{f,side}$ , and Nu may differ under different system assumptions.

The value of the convective heat transfer along the microchannels (i.e., current) is represented as follows (Sridhar et al., 2013a):

$$J_{conv} = c_{conv} (T_{south} - T_{north}), \qquad (2.7)$$

where  $T_{south}$  and  $T_{north}$  are the temperatures at the south and north surfaces of the grid cell.  $c_{conv}$  is the liquid convection coefficient, which is defined as  $C_v u_{avg,y} \Delta A_y$ .  $C_v$  is the specific heat capacity,  $u_{avg,y}$  is the average liquid flow velocity and  $\Delta A_y = wh$ . The inlet temperature of the coolant is the boundary condition for this model.

Kaplan *et al.* has validated the 4RM-based CTM against a liquid cooling via microchannels COMSOL model (Kaplan et al., 2017). They ran steady-state simulations for a range of heat flux values of 12.5, 25, 50, and  $100 W/cm^2$  as well as for different flow velocities = 0.5, 1.0, 1.5, 2.0 *m/s*, and record the maximum temperature of the processing layer for the 4RM-based CTM and COMSOL. Compared to COMSOL simulations, the 4RM-based CTM has a maximum error of 2.8% with a speedup of 43300×.

To further speed up the simulation time of the liquid cooling via microchannels, a 2-resistor model-based (2RM-based) CTM has been designed in the previous work (Sridhar et al., 2010). In the 4RM-based CTM, the thermal cells' boundaries to conform to the solid-liquid interfaces need to be defined, which results in very fine discretization and consequently prohibitively large simulation time. The 2RM-based CTM solves this problem by homogenizing the whole microchannel layer into a single porous medium. In this way, thermal cells are no longer constrained by microchannel dimensions, and even multiple microchannels are covered by a single thermal cell in this homogeneous medium. Sridhar *et al.* (Sridhar et al., 2014) compared the simulation speed and accuracy of 4RM-based CTM and 2RM-based CTM of liquid cooling via microchannels on test 3D chips. The simulation results show that 2RM-based CTM achieves a  $375 \times$  speedup compared to 4RM-based CTM, with an accuracy loss of 7%.

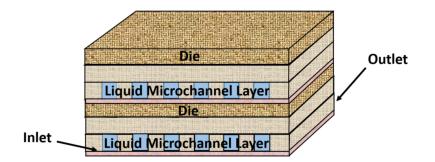

# 2.2.3 Hybrid Cooling

Hybrid cooling refers to incorporating two or more cooling solutions on the same platform. For example, a hybrid cooling system can be designed using liquid cooling via microchannels and TECs. Using liquid cooling via microchannels effectively removes the background heat on large chips and 3D-stacked architectures. However, as the liquid flows through the microchannels, it gets hotter, and the ability to remove heat further decreases. TEC is favorable for handling high power densities in a small area. But the additional cooling power cost is substantially increased when cooling a large area. In this case, a hybrid cooling strategy that combines the strengths of liquid cooling via microchannels and TEC provides much better cooling efficiency. A group of works focuses on using TECs to target the hot spots and liquid cooling via microchannels to remove the background heat (Sahu et al., 2014; Yazawa et al., 2012; Hu et al., 2013). A typical hybrid cooling method using TEC and liquid cooling via microchannels is shown in Figure 2.6.

Figure 2.6: Front view of a hybrid cooling design (Kaplan et al., 2019).

There are several ways to create CTMs for hybrid cooling (liquid cooling via microchannels and TEC). One approach is to use a high HTC value to represent liquid cooling via microchannels in addition to a TEC CTM to model hybrid cooling (Yazawa et al., 2012). This method shows a  $10 \times$  cooling power reduction when compared to using only liquid cooling via microchannels (Yazawa et al., 2012). Another way builds a CTM of hybrid cooling using liquid cooling via microchannels CTM and TEC CTM (Kaplan et al., 2019). This method incorporates the CTMs for liquid cooling via microchannels and TEC from a previous work (Kaplan et al., 2017). Kaplan *et al.* validated the accuracy of this hybrid cooling CTM against COMSOL simulations. This hybrid cooling CTM achieves a  $1607 \times$  speedup with a max error of less than  $5.7^{\circ}$ C.

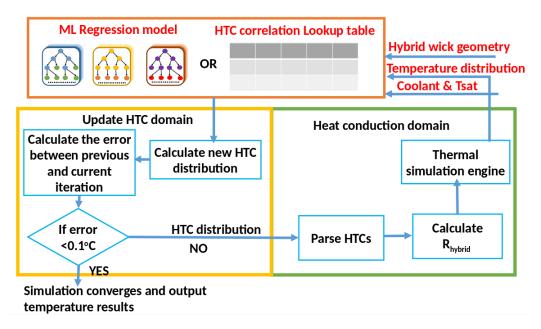

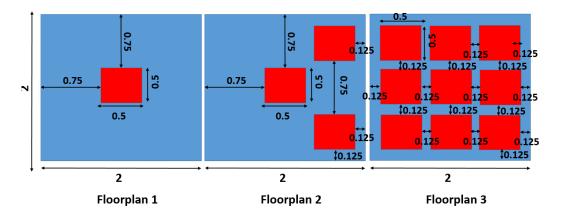

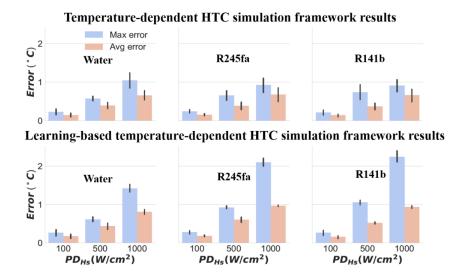

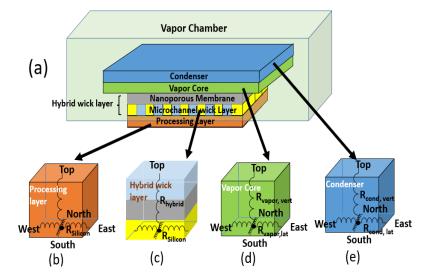

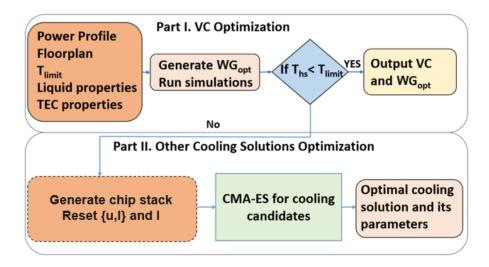

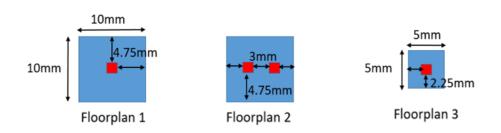

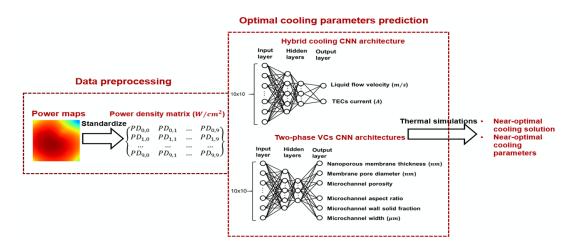

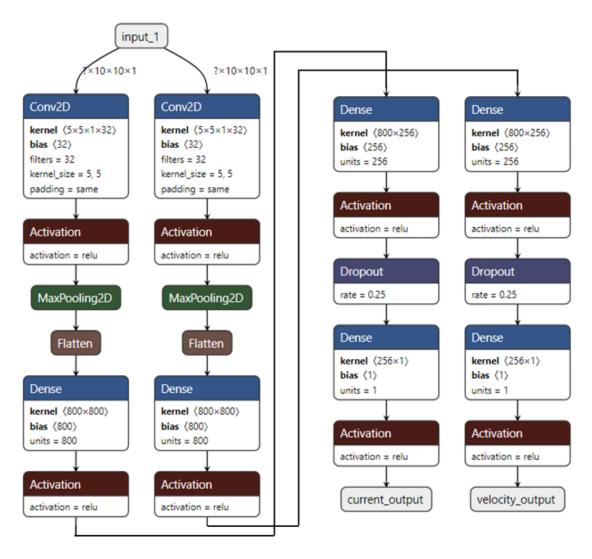

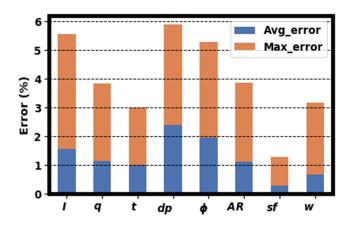

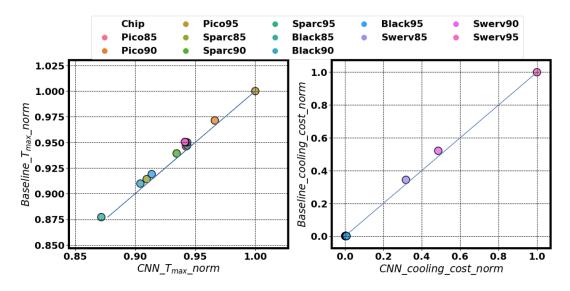

# 2.3 Cooling Optimization Methods