### LYRA : A HIGH LEVEL MODELING AND SYNTHESIS METHODOLOGY FOR CONCURRENT SYSTEMS USING RENDEZVOUS

VYAS VENKATARAMAN

Dissertation submitted in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

## BOSTON UNIVERSITY COLLEGE OF ENGINEERING

Dissertation

# LYRA : A HIGH LEVEL MODELING AND SYNTHESIS METHODOLOGY FOR CONCURRENT SYSTEMS USING RENDEZVOUS

by

### VYAS VENKATARAMAN

M.S., Boston University, 2008

Submitted in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

2012

© Copyright by VYAS VENKATARAMAN 2010

### Approved by

First Reader

Martin Herbordt, PhD Associate Professor of Electrical and Computer Engineering

Second Reader

Wei Qin, PhD Senior Software Developer, Tower Research Capital, LLC

Third Reader

Jayanta Bhadra, PhD Manager, Verification Tools and Flows, Freescale Semiconductor Inc.

Fourth Reader

Ayse Coskun, PhD Assistant Professor of Electrical and Computer Engineering

#### Acknowledgments

I would like to thank Dr. Alexander Taubin for sparking my interest in the area of digital hardware design and for his guidance. My thanks also to Dr. Wei Qin for introducing me to the field of communication abstraction and co design and for his mentorship. Thanks also to Dr. Martin Herbordt for his patience and insight into polishing and improving this work, and Dr. Jayanta Bhadra for his industry related feedback that allowed this work to be more relevant. Additionally, thanks to Dr. Ayse Coskun for serving on the defense and Dr. Doug Densmore for his valuable counsel. I would like to thank the help of the ECE office staff, particularly Julie Guthrie.

Finally, I would like to thank my parents and my wife for their constant patience, generosity and unyielding support. Their presence and support has been instrumental throughout the PhD program.

### LYRA : A HIGH LEVEL MODELING AND SYNTHESIS METHODOLOGY FOR CONCURRENT SYSTEMS USING RENDEZVOUS

(Order No.

### VYAS VENKATARAMAN

Boston University, College of Engineering, 2012

Major Professor:MartinHerbordt,PhD,AssociateProfessor of Electrical andComputer Engineering

)

#### ABSTRACT

Since their introduction, modern computer systems have been increasing in complexity. System designers have been dealing with ever larger designs by moving to higher abstraction level system descriptions. The existing register transfer level of abstraction has become unable to handle modern designs, requiring a move to high level modeling. The most popular of the current approaches for high level design is using SystemC, a set of libraries built in C++, to model hardware using software concepts. However, software based approaches suffer from a major drawback - the lack of a formal definition for both communication and computation. Basic hardware primitives such as concurrency and multiparty communication cannot be easily expressed in software and the translation of these models into hardware equivalents is difficult. As a result, most designers choose to represent systems as a high level SystemC model for simulation, and a set of register transfer level designs for implementation. This gap presents challenges in the design and verification of the system.

This work proposes a novel high level modeling methodology, called Lyra, which

uses the well studied concepts of finite state machines for computation and of rendezvous for communication. A rendezvous is a bidirectional, atomic, synchronous communication construct that supports a wide variety of communication patterns such as multiparty and variable party communication. The presence of a novel mechanism to handle nondeterminism from the use of rendezvous allows Lyra to model designs that existing rendezvous based approaches cannot. Finite state machine based modeling makes Lyra amenable to hardware implementation and easily understandable by hardware engineers. The formal foundation of Lyra and the ability to implement models as hardware are advantages compared to other high level modeling approaches.

This thesis presents Lyra and the novel rendezvous nondeterminism resolution mechanism, called the communication scheduler. It develops a graph based method to analyze and compare different rendezvous based approaches. This work demonstrates the implementation of Lyra into a simulator and a synthesis tool, creating a practical design flow. This work examines some system models that demonstrate the benefits of using Lyra.

### Contents

| 1        | Introduction |                                                                                                  |    |

|----------|--------------|--------------------------------------------------------------------------------------------------|----|

|          | 1.1          | Introduction to Electronic Design Automation (EDA)                                               | 2  |

|          | 1.2          | Introduction to Synthesis                                                                        | 8  |

|          | 1.3          | Motivation                                                                                       | 12 |

| <b>2</b> | Rela         | ated Work                                                                                        | 19 |

|          | 2.1          | High Level Synthesis                                                                             | 19 |

|          | 2.2          | High Level Synthesis Methodologies                                                               | 20 |

|          | 2.3          | Properties for High Level Synthesis                                                              | 23 |

|          | 2.4          | Differences between Hardware Description Languages (HDLs) and soft-                              |    |

|          |              | ware programming languages                                                                       | 26 |

|          | 2.5          | Nondeterminism                                                                                   | 28 |

|          | 2.6          | $C/C++$ Based approaches $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 29 |

|          | 2.7          | Introduction to Rendezvous                                                                       | 34 |

|          | 2.8          | Nondeterminism using Rendezvous                                                                  | 38 |

|          | 2.9          | Rendezvous Based Approaches                                                                      | 39 |

|          | 2.10         | Other High Level Approaches                                                                      | 42 |

| 3        | Lyra         | a: An Introduction                                                                               | 45 |

|          | 3.1          | An Overview                                                                                      | 45 |

|          | 3.2          | Description of Lyra                                                                              | 46 |

|          | 3.3          | The need for nondeterminism in Lyra                                                              | 49 |

|          | 3.4          | Communication Scheduling                                                                         | 50 |

| 4        | $\mathbf{Sch}$   | eduling 5                                        |     |  |

|----------|------------------|--------------------------------------------------|-----|--|

|          | 4.1              | Overview of Scheduling                           |     |  |

|          | 4.2              | Properties of Scheduling                         |     |  |

|          | 4.3              | Policies                                         | 55  |  |

| <b>5</b> | Gra              | ph Based Tools                                   | 57  |  |

|          | 5.1              | Graphical Analysis of Process Networks           |     |  |

|          | 5.2              | 2 Transition Relation Graph (TRG)                |     |  |

|          | 5.3              | Minimal Candidate Schedules (MCS)                | 64  |  |

|          | 5.4              | Occurrence Relationship Graph (ORG)              | 70  |  |

|          | 5.5              | Policy Implementation                            | 72  |  |

|          |                  | 5.5.1 Global Weight Optimal Policy               | 73  |  |

|          |                  | 5.5.2 Static Local Weight Ordering Policy        | 78  |  |

| 6        | For              | rmal Notation                                    |     |  |

|          | 6.1              | Basic Concepts                                   | 80  |  |

|          | 6.2              | 2 Lyra Formalization                             |     |  |

|          | 6.3              | Graphical Tool Algorithms                        |     |  |

|          | 6.4              | Scheduler Description                            |     |  |

|          | 6.5              | Implementation                                   | 95  |  |

| 7        | 7 Lyra Tool Flow |                                                  | 97  |  |

|          | 7.1              | Overview of the Lyra tool flow                   | 97  |  |

|          | 7.2              | Simulator                                        | 98  |  |

|          | 7.3              | Synthesis                                        |     |  |

|          |                  | 7.3.1 Overview of Approach to Hardware Synthesis | 99  |  |

|          |                  | 7.3.2 ORG Node Creation                          | 102 |  |

|          |                  | 7.3.3 Policy Mapping                             | 104 |  |

|          |                  | 7.3.4 Other considerations for Synthesis         | 104 |  |

| 8                        | Con                                | mparison to Other Approaches 10           |     |  |  |

|--------------------------|------------------------------------|-------------------------------------------|-----|--|--|

|                          | 8.1 Effects of Rendezvous Features |                                           | 107 |  |  |

|                          | 8.2                                | Graphical Analysis                        | 109 |  |  |

| 9                        | An                                 | empirical example of a Lyra based system  | 111 |  |  |

|                          | 9.1 Introduction                   |                                           |     |  |  |

|                          | 9.2                                | PCI Express Model                         |     |  |  |

|                          |                                    | 9.2.1 PCI Express Overview                | 112 |  |  |

|                          |                                    | 9.2.2 Overview of the Lyra implementation | 113 |  |  |

|                          |                                    | 9.2.3 Port Module                         | 114 |  |  |

|                          |                                    | 9.2.4 PCI Express Endpoint                | 116 |  |  |

|                          |                                    | 9.2.5 PCI Express Switch                  | 117 |  |  |

|                          |                                    | 9.2.6 PCI Express Root Complex            | 117 |  |  |

|                          | 9.3                                | .3 ADL Model                              |     |  |  |

|                          | 9.4                                | Integration                               |     |  |  |

|                          | 9.5                                | .5 Results                                |     |  |  |

| 10 Empirical Results 124 |                                    |                                           |     |  |  |

|                          | 10.1 Empirical Result Overview     |                                           |     |  |  |

|                          | 10.2                               | Models                                    | 124 |  |  |

|                          |                                    | 10.2.1 Elastic Buffer Pipeline            | 125 |  |  |

|                          |                                    | 10.2.2 PCI Express Simplified             | 126 |  |  |

|                          |                                    | 10.2.3 Synchronous MIPS                   | 126 |  |  |

|                          |                                    | 10.2.4 Asynchronous MIPS                  | 127 |  |  |

|                          | 10.2.5 JPEG Encoder                |                                           |     |  |  |

|                          | 10.3                               | .0.3 Scheduling approaches 12             |     |  |  |

|                          | 10.4                               | Result Summary                            | 131 |  |  |

| 11 Conclusions and Future Work |     |

|--------------------------------|-----|

| 11.1 Conclusion                | 135 |

| References                     | 138 |

| Curriculum Vitae               | 145 |

### List of Tables

| 2.1  | High level design criteria | 24  |

|------|----------------------------|-----|

| 2.2  | Approaches to HLS          | 31  |

| 2.3  | Feature Comparison         | 40  |

| 10.1 | Scheduler Search Spaces    | 132 |

| 10.2 | Scheduler Search Spaces    | 134 |

## List of Figures

| 1.1         | Three domains of design                           | 3   |

|-------------|---------------------------------------------------|-----|

| $1 \cdot 2$ | Communication in a complex system                 | 7   |

| 1.3         | Traditional RTL Design Flow                       | 11  |

| $1 \cdot 4$ | Abstraction Levels                                | 13  |

| $2 \cdot 1$ | An Example Process Network                        | 36  |

| $2 \cdot 2$ | Decomposition of Variability                      | 37  |

| $2 \cdot 3$ | Unresolved Nondeterminism                         | 41  |

| 3.1         | Synchronous data flow example                     | 47  |

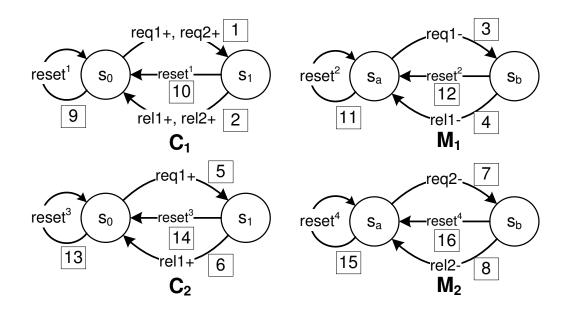

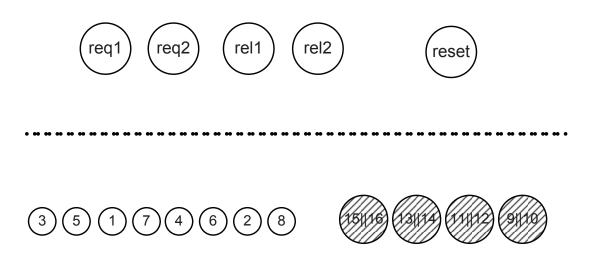

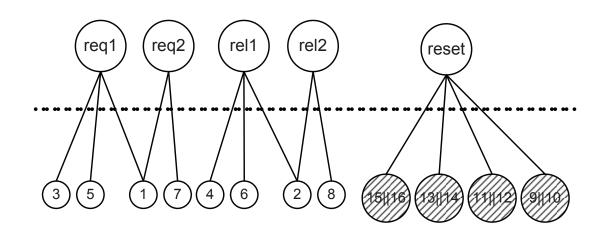

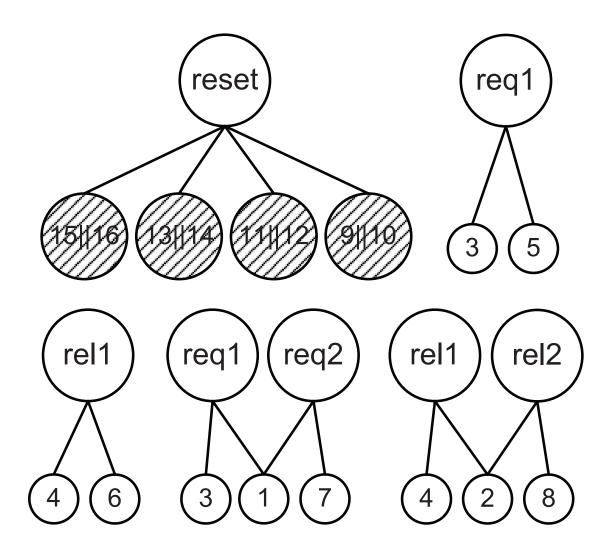

| 5.1         | Annotated Example Process Network                 | 60  |

| $5 \cdot 2$ | Vertices in the TRG                               | 60  |

| $5 \cdot 3$ | Adding Solid edges in the TRG                     | 61  |

| $5 \cdot 4$ | Final TRG                                         | 62  |

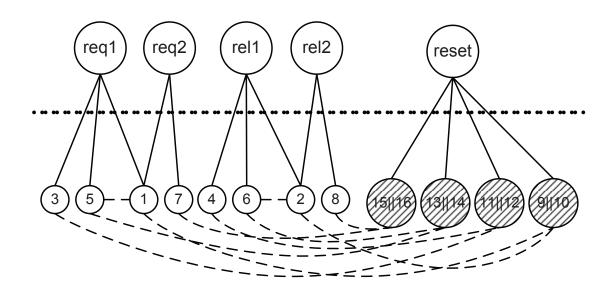

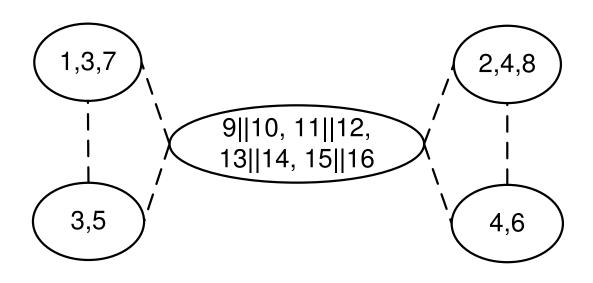

| 5.5         | Minimal Candidate Schedules in the system         | 68  |

| $5 \cdot 6$ | Occurrence Relationship Graph                     | 71  |

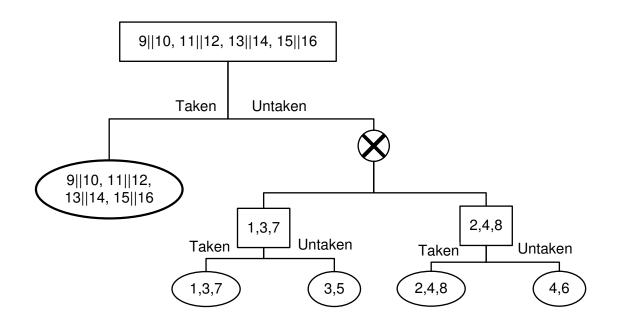

| 5.7         | Tree for GWO policy scheduling                    | 75  |

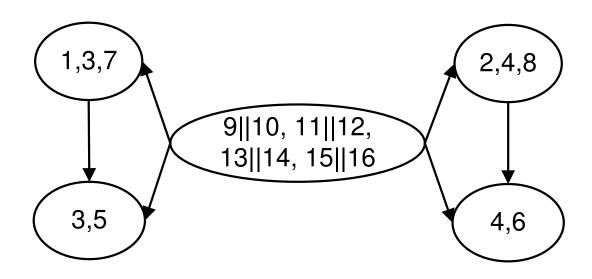

| 5.8         | Directed Acyclic Graph for SLWO policy scheduling | 78  |

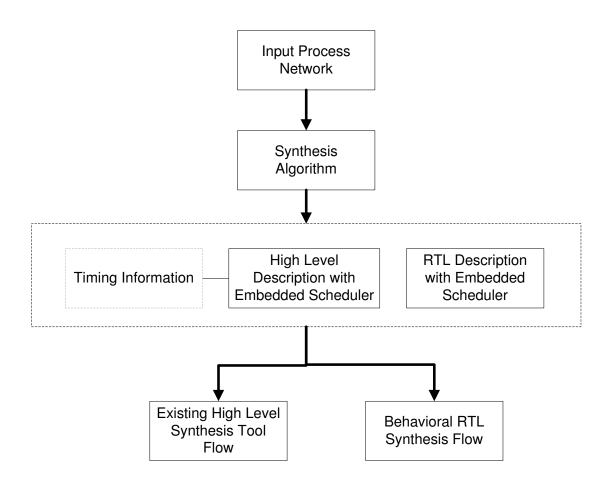

| $7 \cdot 1$ | High Level Overview of Synthesis Flow             | 100 |

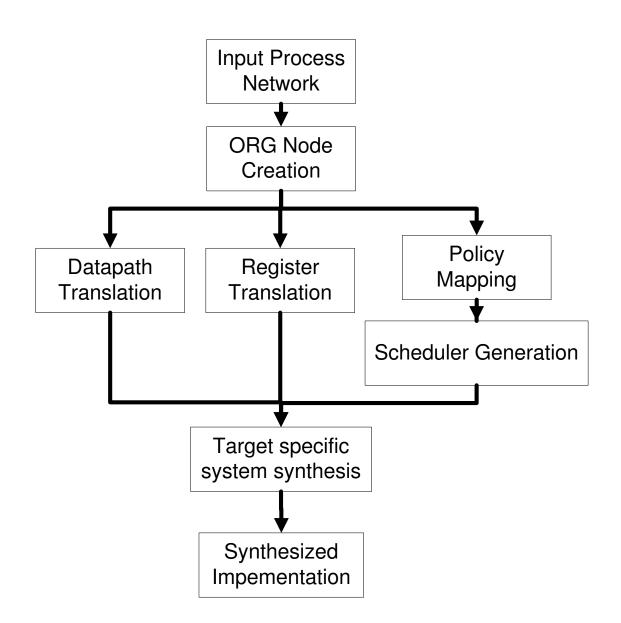

| $7 \cdot 2$ | Detailed view of Synthesis Flow                   | 101 |

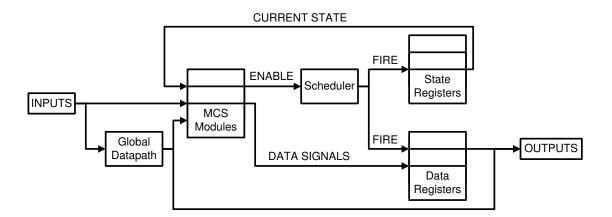

| $7 \cdot 3$ | A general synthesized system                      | 102 |

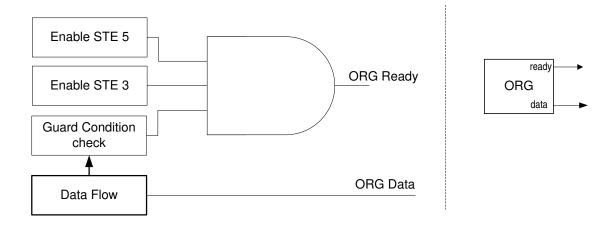

| $7 \cdot 4$ | Synthesis of ORG Nodes                            | 103 |

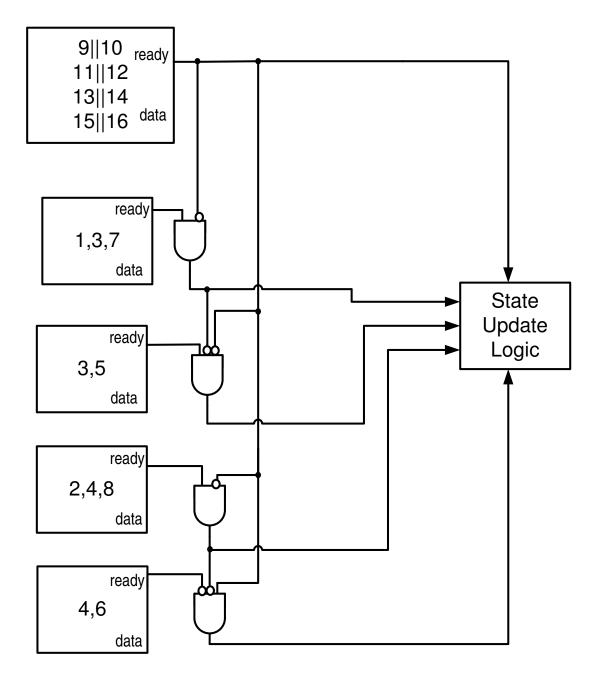

| 7.5         | Synthesized scheduler using SLWO policy | 105 |

|-------------|-----------------------------------------|-----|

| 8.1         | Complexity Increase due to conjunction  | 109 |

| 9.1         | PCI Express Network Topology            | 114 |

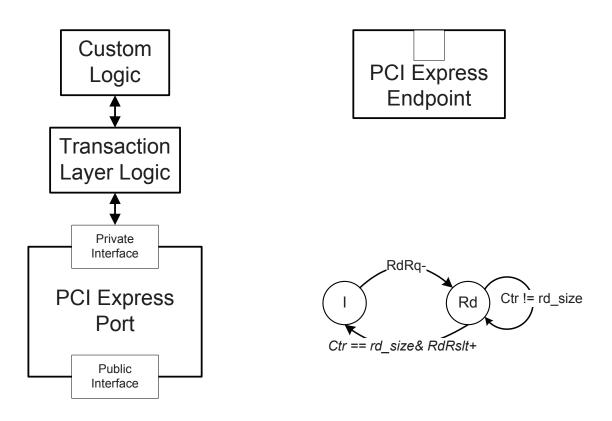

| $9 \cdot 2$ | PCI Express Port Model                  | 115 |

| 9.3         | PCI Express Endpoint                    | 116 |

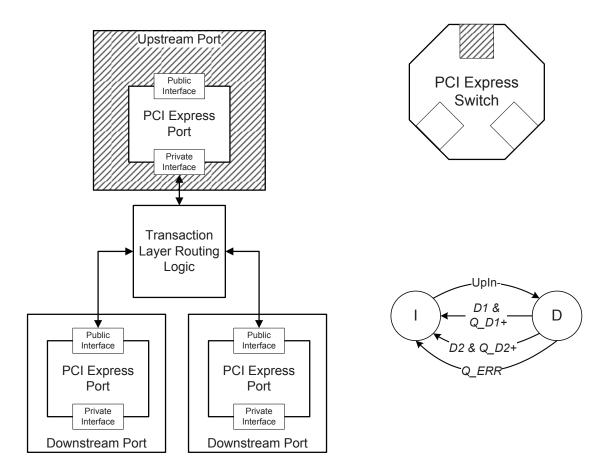

| 9.4         | PCI Express Switch                      | 118 |

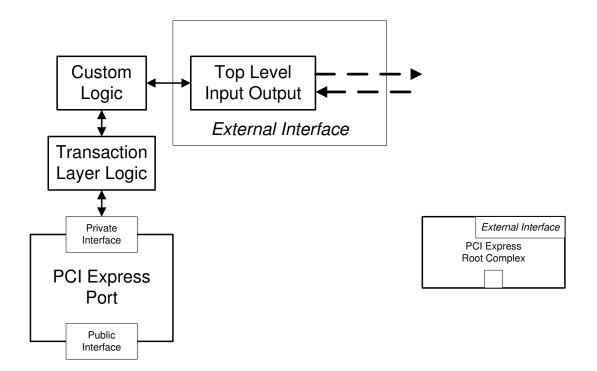

| 9.5         | PCI Express Root Complex                | 119 |

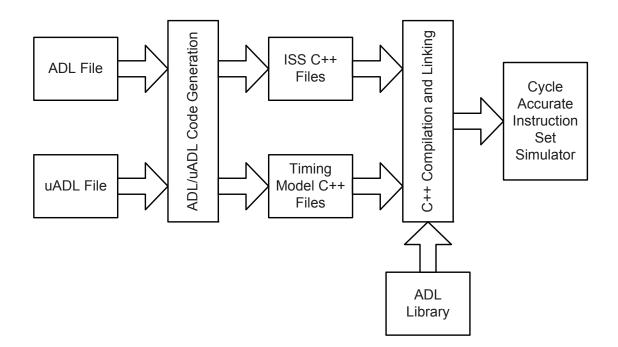

| 9.6         | ADL Design Flow                         | 120 |

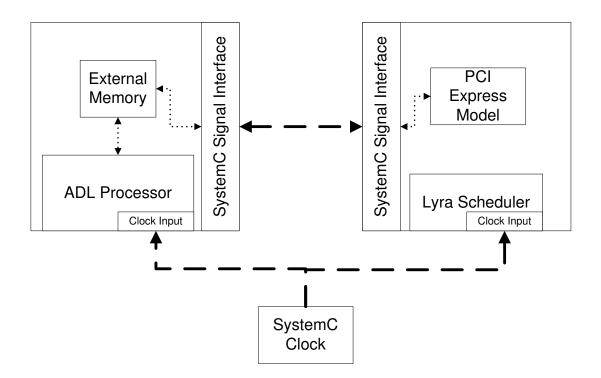

| 9.7         | Integrated System Overview              | 122 |

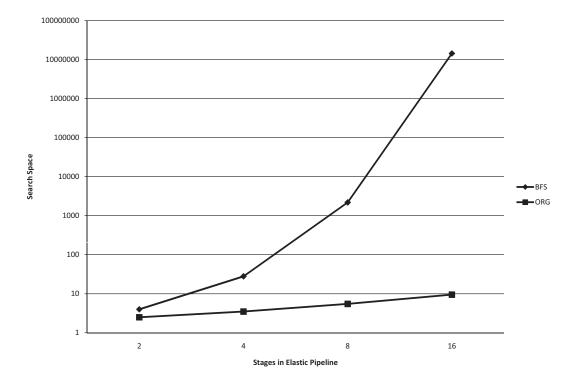

| 10.1        | Complexity comparison                   | 133 |

### List of Abbreviations

| CAD                  | <br>Computer-Aided Design                   |

|----------------------|---------------------------------------------|

| $\mathbf{CCS}$       | <br>Calculus of Communication Systems       |

| $\operatorname{CSP}$ | <br>Communicating Sequential Processes      |

| DFA                  | <br>Deterministic Finite Automaton          |

| DME                  | <br>Deterministically Mutually Exclusive    |

| EDA                  | <br>Electronic Design Automation            |

| EFSM                 | <br>Extended Finite State Machine           |

| FSM                  | <br>Finite State Machine                    |

| GTL                  | <br>Gate Transfer Level                     |

| GWO                  | <br>Global Weight Optimal                   |

| HDL                  | <br>Hardware Design Language                |

| HLS                  | <br>High Level Synthesis                    |

| MCS                  | <br>Minimal Candidate Schedule              |

| ME                   | <br>Mutual Exclusion / Mutually Exclusive   |

| NFA                  | <br>Nondeterministic Finite State Machine   |

| NME                  | <br>Nondeterministically Mutually Exclusive |

| ORG                  | <br>Occurrence Relationship Graph           |

| RTL                  | <br>Register Transfer Level                 |

| SLWO                 | <br>Static Local Weight Ordering            |

| TE                   | <br>Transition Edge                         |

| TLM                  | <br>Transaction Level Modeling              |

| TRG                  | <br>Transition Relationship Graph           |

# Chapter 1 Introduction

Any digital hardware design can be partitioned into two components : computation and communication. Computation refers to the portion of the hardware design dedicated to the transformation of input data to output. The communication component refers to the transfer and synchronization of data between the different computation components. With the increase in complexity of modern hardware systems, there has been a corresponding increase in the complexity of their descriptions. This rising complexity has been contained by simultaneously increasing the level of abstraction of the basic units. By dealing with more abstract representations, larger designs can be modeled and created. While the level of abstraction of computation has been rising over time, the same has not been the case for communication. As a result, in the design of modern digital hardware systems, communication abstraction is increasingly important.

This chapter contains a brief overview of the general concepts in modern digital hardware design, followed by a description of design automation tools and an overview of hardware synthesis. We demonstrate the increasing importance of communication abstraction in behavioral models of digital hardware and briefly describe the solution proposed in this dissertation called Lyra.

#### 1.1 Introduction to Electronic Design Automation (EDA)

Digital electronic circuits, based on the switching activity of transistors are capable of performing complex calculations. When the first integrated circuit (IC), demonstrated in 1958, it could accommodate only a few transistors on it, and could be entirely designed manually. The complexity of modern digital electronics has far exceeded the scale at which manual design of transistors is possible. In 2011, the 32nm Intel i7 processor, for example, contains over 1.17 billion transistors [Kurd et al., 2010]. In order to handle the design and implementation of such large digital hardware designs, automated tools were developed that comprise the Electronic Design Automation (EDA) field.

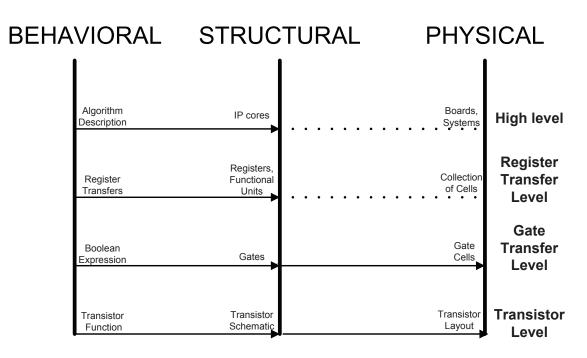

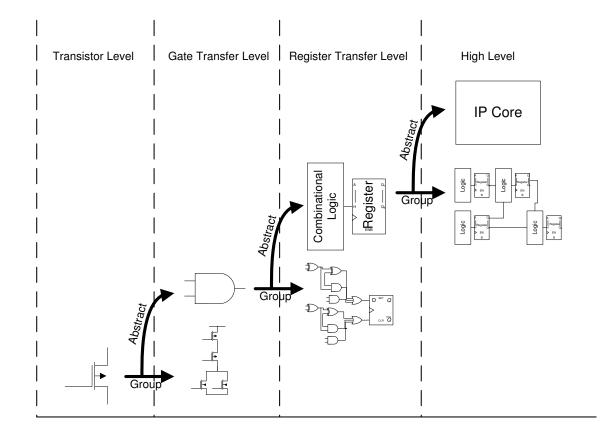

The representations of a digital system can be divided into 3 main domains : the physical, the structural and the behavioral [Gajski et al., 1992]. Within each domain, we have corresponding *levels of abstraction* forming a hierarchy from simpler to more complex, with each succeeding level using the previous one as its basic element (Figure 1·1). The most basic digital hardware design element, at the lowest level of abstraction, is the transistor [Gajski and Ramachandran, 1994]. In the physical domain, the transistor is represented simply by a transistor layout. A *layout* is actual physical shape of the transistor as created in silicon. In the structural domain, the representation is as a symbol. In the behavioral domain, the representation of the transistor is the "on-off" electrical characteristics of the transistor. A transistor can be equivalently expressed in these 3 domains, with the choice of the domain being the use of the design. For a fabrication facility, which creates physical chips, the most relevant representation is the layout. When identifying connections in a digital system, the most useful representation is the structural. When modeling a system, engineers represent the transistor in its behavioral form.

Moving to the next level of abstraction, we have the gate level model, sometimes

**Figure 1.1:** The three domains of design at different abstraction levels. Electronic design automation tools for digital hardware accept a description in the behavioral domain and finally transform them into the physical domain. *Synthesis* is transformation from the behavioral to the structural domain. *Refinement* is the transformation within a domain from a higher level of abstraction to a lower one. *Optimization* is the transformation within a domain at the same level of abstraction, but producing a description that is improved for some target criterion. This is based on the Gajski Kuhn Y chart [Gajski et al., 1992]

called the Gate Transfer Level(GTL). This corresponds to layout cells in the physical domain, to gate schematics in the structural domain and to the boolean expression in the behavioral domain. In each domain, this level can be thought of as replacing a collection of transistor level representations. Thus, a layout cell contains the layouts for multiple transistors. The gate schematic is a representation of multiple transistor schematics. The boolean expression represents the behavior of multiple transistors.

For higher levels of abstraction, the tight correspondence between the various domains weakens. Higher abstraction levels do not always require the introduction of new elements in the physical and structural domains. The descriptions of gates usually occurs as a *netlist*, a structural list of gates and their connection.

The next level of abstraction, the register transfer level (RTL) can best be described as a collection of gates that feed registers. The correspondence in the physical and structural domains is to collection of cells and a collection of combinational gates and clocked state holding elements respectively. In the behavioral domain, the correspondence is to a new style of design where data is processed sequentially in time. This new design style raises the level of abstraction by breaking apart the design into smaller elements that can be designed in parallel and perform computation in a pipelined fashion. Each piece of the design is combinational, but performs actions on data obtained from and sent to registers. In effect, the RTL system can be described in the behavioral domain using a state chart or as a set of register transfer equations.

Hardware Description Languages (HDLs) such as Verilog [IEEE, 2001] or VHDL [IEEE, 2000] are used to define the behavioral input. These languages differ from software programming languages in their assumptions about concurrency, communication and data type handling. Both HDLs and software programming languages support basic concepts such as modularity. Modularity refers to the ability to wrap elements representing computation and storage into block referred to as a *module*. This allows

for reuse of a piece of a design and hierarchical design, by allowing one module to contain *instances* of other modules, allowing for larger designs. On the other hand, HDLs and software programming languages differ in some basic ways. In software programming languages, which assume sequential execution, concurrency must be defined explicitly. HDLs, on the other hand, have an implicit notion of concurrency with each module independent of the other. The difference in handling concurrency affects the basic communication constructs supported by these approaches. Software programming languages generally use function calls as the basic mechanism of communication. In contrast, HDLs generally use wires as the basic communication primitive. The loose semantic definitions of function calls, and their use of features like recursion, variable length arguments prevent them from being easily converted into a hardware equivalent. Finally, the basic datatypes in HDLs are very different from those in software programming. While some types are common, software programming data types often depend on the architecture of the underlying processor as bit widths are not often defined. HDLs, on the other hand, fix the size of data types rigidly to ensure that they are always easily relateable to hardware. These distinctions are further elaborated in Chapter 2.

At present, the level of abstraction that is being used is the system level [Sangiovanni-Vincentelli, 2003] [Densmore et al., 2006]. Elements at this level correspond to *cores* that frequently are actually presented as a collection of RTL elements in the structural domain. These high level models are usually referred to as Intellectual Property cores (IP cores) [Gajski et al., 2000a] or as *soft cores*. This reflects the fact that the tasks of modern system designers has become integrating different functional blocks from multiple sources. In the behavioral domain, this level of abstraction corresponds to well defined algorithm implementations as extended communicating state machines. In a sign of the growing complexity of modern com-

puter systems, there is a disconnect between the behavioral and structural domains [Hemani, 2004]. The behavioral model at this level of abstraction is usually modeled using software programming techniques, but as the structural model is RTL, there is some extra effort that needs to be expended by the designer to create both representations.

Increasing the abstraction level has been acknowledged as an essential method used by modern EDA tools to handle increasingly complex systems [Sangiovanni-Vincentelli, 2003] [Hemani, 2004]. The abstraction of computation is the primary focus for the increases in the levels of abstraction [MacMillen et al., 2000]. Abstraction of communication, on the other hand, has become increasingly important as the primary driver for the future of EDA tool design [Hemani, 2004] [Kumar et al., 2002] [Pestana et al., 2004]. We see that computation has moved in abstraction from being modeled by transistors to gates to registers to IP Cores. Communication, on the other hand, has existed as wires in the first three levels of abstraction, with no clear agreement on its abstraction in the high level era. This presents major challenges for the modern era that may have several IP cores communicating with each other, such as the Network-On-Chip style of design [Hemani et al., 2000] [Pestana et al., 2002] [Gerstlauer et al., 2005].

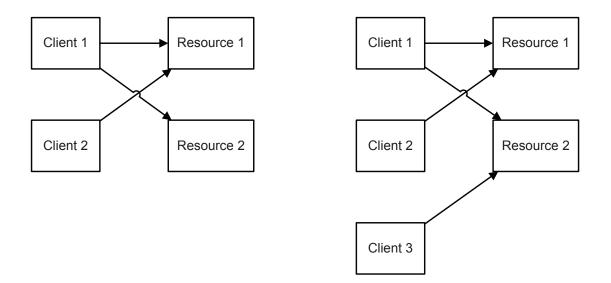

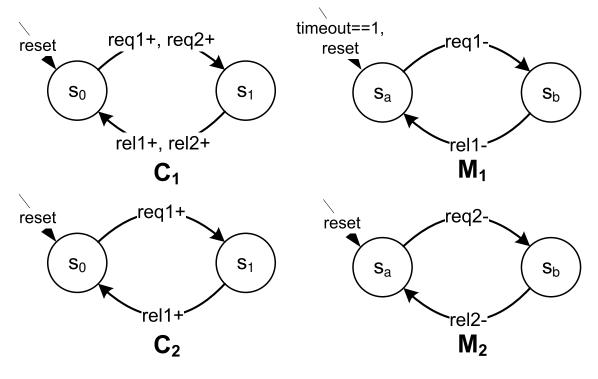

A practical example of the use of abstraction for communication can be demonstrated in Figure 1.2. In the definition of a system on chip, there is a need to model different patterns of communication between IP blocks. In this scenario, there are two clients, simulating processors capable of complex behaviors and two resources, modeling hardware co-processors, such as a cryptographic decoder. The clients are capable of requesting and acquiring resources. The resources are first requested, exclusively assigned to a single client and then released. The first client attempts to request and use both resources. The second client requests just the first resource.

Figure 1.2: A sample of a scenario that demonstrates the need for communication flexibility. If we have a system-on-chip where there are two clients that can request and exclusively use the resources (shown on the left), the abstraction of communication can allow for easy modeling of scenarios, such as the addition of a client (shown on the right)

At any time, one, or both clients could attempt to request to acquire the resources. The communication mechanism should be abstracted in a fashion so that it can be easily express patterns such as a client requesting multiple resources, or model the conflicting access to a resource. At the same time, the abstraction should be general enough to allow for the easy addition of new clients or resources, while avoiding the specification of details about how the request mechanism is implemented. In a purely software implementation of system, the addition of a new client can be as simple as adding a function call. The operating system provides high level communication and synchronization primitives that can be used to implement the communication. In a hardware implementation, however, this new client will require the addition of extra computation capability as well as wires to handle the new data transfer path and to arbitrate between the clients. The addition of this new hardware in turn affects the communication path. As a result, any such addition requires extensive redesign, even of parts of the design that are not directly affected. In this case, the addition of this new client will affect the hardware implementation of the second resource, which in turn will affect the design of other clients that may need to communicate with it.

Modern hardware designs, such as Network-on-chip and system-on-chip, take full advantage of the high abstraction level of computation to express complex systems. However, the lack of a corresponding clear high level abstraction for communication in digital hardware design presents a major challenge [Hemani et al., 2000] [Pestana et al., 2004] [Kumar et al., 2002] [Gerstlauer et al., 2005].

In this work, we address the problem of the lack of a useful communication abstraction for high level design of computer hardware. The proposed solution we present is a novel approach to high level computer system design. This methodology uses a communication and synchronization abstraction, that is as abstract as communication primitives used in software design. This abstraction is flexible enough to model a wide variety of different communication patterns. The solution we propose differs from previous approaches as it allows the designer to use a variety of features without restriction, such as multiparty communication and variable party communication. In addition, features like conjunction and disjunction of synchronization events and the composition of these primitives are fully supported. A novel communication scheduler enables the generation of structures that can greatly speed up simulation and allow for hardware synthesis of models described using this methodology. Further, a strong underlying formal model enables the creation of model checking and design verification tools.

#### **1.2** Introduction to Synthesis

Circuits described using GTL, or at the gate level can be created manually for small systems, and until the late 1970's this was the norm. As the circuit complexity grows,

there arises the need for the move to RTL descriptions of circuits. A survey done in 1975 about the then emerging field of Register Transfer Level design [Barbacci, 1975] was one of the first to define the synthesis of a system as the conversion of a symbolic representation to a physical one. Gajski et. al. created a graphical aid to visualize the relationships between the domains of design [Gajski et al., 1992]. In terms of the domains in Figure 1.1, the arrows from the behavioral to the structural represent synthesis. The creation of a gate or transistor level structural description is called physical synthesis. RTL synthesis involves the generation of clocked registers and combinational circuits from a series of register transfers.

Finally, at the system level, *high level synthesis* involves the generation of complex structures from algorithm or software behavioral descriptions[Gajski et al., 1992]. While synthesis alone moves from one domain to another at the same level of abstraction, another important ability is to move from a higher abstraction level to a lower one in the same domain. This ability is referred to as *refinement*. In the structural domain, each subsequent level of abstraction is defined as a collection of elements from the lower one. For example, a gate is a collection of transistors, or a register and its update logic is a collection of gates. As a result, design refinement in the structural domain consists of replacing a higher abstraction level component with the group of lower abstraction level components that make it up. A final transformation is *optimization*, which refers to the improvement of a design in the same domain, within the same abstraction level utilizing some target characteristic. A common example of this would be the area and timing optimizations that are performed on designs.

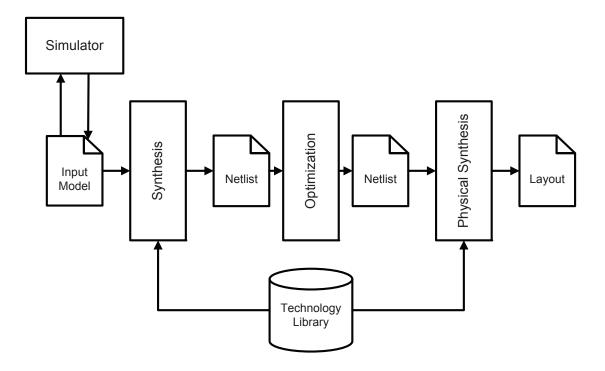

Tools in the EDA field cover all three domains and primarily exist perform one of the three transformations : synthesis, refinement or optimization. As all circuits eventually need to be converted to a physical representation, we can conceive of the design process as starting by defining the behavioral domain representation of a system at a high level of abstraction. Then, utilizing a set of tools, a structural description at the same level is generated. Finally, these descriptions are moved down the levels of abstraction until a physical domain transistor level circuit is obtained. This represents the *design flow*. The traditional design flow, especially for RTL circuits is seen here in Figure 1.3.

The idea of generating hardware from software-like descriptions was proposed in [Mead and Conway, 1980]. The steady increases in the level of abstraction were helpful in the creation of new tools and methodologies. First, tools for synthesis from each abstraction level were created and then used as the base components for the next abstraction level. As a result, valuable work done previously for tasks like area based optimization or physical place and route for layout is reused by methodologies that work at higher levels. Further, it meant that newly created tools only needed to establish a way to convert the input behavioral description into a structural description that could be reduced to the next lower level of abstraction.

The currently used synthesis methodology can be seen in Figure 1.3. The designer creates a behavioral description of a system in a RTL HDL such as Verilog or VHDL. By simulating the design, its behavior can be verified, leading to its iterative improvement. Once satisfied, the design is passed to the synthesis tool, which applies information about the technology library to create a netlist. This *netlist* is a gate level structural description of the circuit. It is passed through an optimization step to create an optimized netlist. Finally, the netlist is passed through the physical synthesis tools, which can create a complete layout from a basic gate layout, and then place and route wiring. The basic cell layout can come from the technology library or can be created by the user. Automated place and route tools use the user defined cells to generate a complete layout for the system and create wiring to connect these

**Figure 1.3:** Traditional design flow for Register Transfer Level descriptions. The input is a register transfer level behavioral specification created in a HDL like Verilog or VHDL. The first step of the process generates a gate level structural netlist. After optimization, this netlist is used to generate a physical transistor level layout.

cells. This will create a functional physical layout for the whole model. A sequence of steps, where data is sequentially processed by a series of tools, is referred to as a *tool flow*. This presents a RTL synthesis tool flow.

The size of modern systems has been continuously rising, along with the design effort necessary. This makes the move of the behavioral description to a higher level than RTL extremely likely. In [Gupta and Brewer, 2008], Gupta et. al. demonstrate the financial benefit of high level design methodologies. They estimate that the design cost of an integrated circuit is US\$15M with the use of tools at abstraction levels higher than RTL, as opposed to almost US\$342M for a pure RTL approach. This is a 20x benefit to using such methods to create circuits, as opposed to the RTL abstraction based design. Modern high level design approaches have been gaining increasing acceptance [Martin and Smith, 2009] and are seen as the most important way to reduce design costs and design effort while simultaneously increasing the system size. In order for any high level design approach to be successful, there are many factors that must be considered, not the least of which is how they abstract communication and the mechanism they provide for the creation of lower abstraction level descriptions.

In Section 2.1, we present the current state of synthesis from high level descriptions and discuss the significant issues preventing their widespread use. In subsequent chapters, we discuss how the novel methodology presented in this dissertation does not suffer from the same drawbacks.

#### 1.3 Motivation

Over the past few decades, successively more abstract models of digital hardware systems have been developed, allowing designers to encapsulate and contain their effective complexity. Beginning with the schematic transistor representations that were used by designers to replace the physical layout, there has been a move towards

Figure 1.4: Levels of abstraction in the structural domain. The level of abstraction to represent computation has been rising, but that of communication has remained fixed.

expanding the gap between the physical and functional representations of a circuit, with each new level built upon the old. An increasing portion of modern design work is done at the system level, where designers are able to simply choose soft cores built by other vendors, that can perform complex computations, and integrate them into one system. The designer's task is to create and model the increasingly complex communication between vendor provided cores.

At the system level of abstraction, there is an open question of what design abstraction should be used and several high level models have been proposed for this purpose. The main focus of abstraction into a higher level model has been in one of two areas : computation and communication. Advances in compiler techniques and high level synthesis (HLS) techniques have provided strong support for high level description of computational tasks. High level modeling of communication and concurrency, on the other hand, has only seen success in special domains such as digital signal processing and synchronous programming. For broader applications, the recent trend of transaction level modeling (TLM)[Cai and Gajski, 2003], characterized by using software function calls for communication and synchronization, has become a prevailing standard. TLM is especially useful for bottom-up assembling of components of various natures into a common modeling framework such as SystemC [Automation, Design and Committee, Standards, 2006]. In software design, communication is performed dynamically, using support from the operating system. Software communication architectures, like message passing, or dynamically created sockets are not viable communication primitives in hardware. As software function calls are fundamentally only a language construct for code reuse and modularity, their use for modeling communication relies on the mechanisms of the underlying operating system, such as scheduling-related system calls and the thread library. In the case of SystemC, this involves the manipulation of the event calendar via the wait() and notify() calls or similar methods. This approach is effective for functional simulation, but is not amenable to hardware synthesis or formal verification. The lack of a good high level way to represent different communication patterns is an increasing problem as designs become larger and communication plays a larger role in system design [Gerstlauer et al., 2005].

The flexibility of high level models in the abstract specification of systems is offset by the difficulty of synthesizing the hardware equivalent of such a description. In survey of the field, Sangiovanni-Vincentelli et. al. describe the "lack of clear unambiguous synthesis semantics" as a hurdle towards the adoption of existing high level methodologies such as SystemC [Sangiovanni-Vincentelli, 2003]. Traditional low level register transfer level (RTL) descriptions are easy to synthesize, but are too detailed to allow for reconfiguration to explore the design space and for functional verification. Thus, modern systems are typically maintained as two separate models. A high level model, in a language such as SystemC, that allows for functional and transactional behavior description and verification. Simultaneously, a low level RTL model must be maintained for behavioral synthesis. This duplication leads to a doubling of design time and effort and presents a semantic gap that is a source for errors and requires additional manual verification.

Recently in the EDA field, there is a renewed interest in using rendezvous for synthesizable system descriptions. A *rendezvous* is a classical communication mechanism for modeling communication. It appears in languages such as Handel-C [Celoxica Ltd, 2003], Haste [de Wit and Peeters, 2006], and most recently, SHIM [Edwards and Tardieu, 2005]. It provides a similar level of abstraction as software functions, but is based on formal foundations such as the Communication Sequential Processes (CSP) [Hoare, 1978] and the Calculus of Communication Systems (CCS) [Evangelist et al., 1989]. More interestingly, rendezvous naturally support multiparty features such as disjunctive and conjunctive composition, which enable the modeling of choice and synchronization among multiple processes. However, due to the difficulty of implementing multiparty schedulers, contemporary rendezvous-based concurrent languages tend to leave out conjunctive composition or even both types of composition.

In this dissertation, we present a solution to the problem of a high level design methodology that is synthesizable. This work utilizes the idea of rendezvous as a powerful communication abstraction mechanism. This methodology, called Lyra, is presented as a series of communicating processes, which can synchronize via rendezvous. The abstract concept of rendezvous are presented concretely using two basic language primitives. The use of abstract rendezvous features are allowed so that designers can easily harness them. For example, rendezvous features such as disjunction are presented as simply multiple ways for the process to make progress. The use of the full range of rendezvous features presents the problem of nondeterminism. Nondeterminism refers to the case where there exist multiple methods for the system to make progress. This is an unavoidable feature in high level languages as it is a side effect of allowing partial specification of a design, an important tool in raising abstraction levels. As raising the abstraction level of communication has only now become a priority, existing approaches choose to resolve nondeterminism at the specification level. Typically, they achieve this by limiting the sources of nondeterminism, i.e. the features of rendezvous being used. Other approaches shift the burden for this resolution on the designer. In contrast, Lyra is capable of modeling complex communication patterns in a succinct fashion. The introduction of a novel communication scheduler allows this approach to be efficient for hardware synthesis while retaining the flexibility of communication primitives. The communication scheduler is able to resolve, at run time, the behavior of the system, and using some optimization criteria, is able to ensure that the system functions in a deadlock free way. The generation of the communication scheduler is based on two major graph based tools. The first, called a *Transition Relation Graph*, is a represention of the relationships between different transition edges in the system and enables the efficient identification of the relationships that can create valid progress. The second, called the *Occurrence Relation Graph*, uses the relationship information to create a graphical representation of the communication complexity of the system and identify the communication problems that need to be resolved. The use of *policies* allow the separation of the heuristic used from the general approach, and present a way for the scheduling approach to resolve the same problem for different criteria. We also propose a *formal model* for Lyra, based on an extension of the Extended Finite State Machine formalism and on the definition of rendezvous. This formal basis is used to create the definition of the communication scheduler and clarifies the advantage of using a policy based approach.

The remainder of the dissertation is organized as follows. Section 2 discusses related work in high level synthesis as well existing rendezvous based design approaches. The solution to the problem of a high level language with a powerful communication abstraction is proposed in Chapter 3. An overview of the communication scheduling mechanism is developed in Chapter 4. The graph based tools for the construction of scheduler and policies for heuristic resolution are presented in Chapter 5. The underlying formal model for Lyra is developed in Chapter 6. A description of the tool flow that implements this methodology is covered in Chapter 7. A short examination of the communication complexity using the graph based tools developed for this approach is examined in Chapter 8. The use of the proposed methodology is demonstrated in Chapter 9 using the empirical example of a large system modeled at multiple abstraction levels. Chapter 10 develops some additional examples, and demonstrates the benefits of using the communication scheduler. Finally, we present some conclusions and future avenues of work in Chapter 11.

# Chapter 2 Related Work

In this chapter, we present an overview of existing digital hardware synthesis from high level behavioral descriptions. We examine some of the fundamental limitations with contemporary approaches for high level modeling of digital hardware systems. We describe the issue of nondeterminism, a fundamental problem in the high level abstraction of communication. We present the concept of rendezvous and describe previous work done on their usage. We describe a system developed for the classification of rendezvous based approaches.

### 2.1 High Level Synthesis

Synthesis is the conversion of a behavioral description into a structural one. This is usually implemented as a program that forms part of a tool flow, a set of programs that accept as input a higher abstraction level behavioral description and produce a lower abstraction level physical representation. High level modeling, where the input behavioral description is at a higher level of abstraction than RTL, is an increasingly important area [Sangiovanni-Vincentelli, 2003]. This form of design description is used mainly for the behavioral specification of entire systems. The increased flexibility at this abstraction level lends itself to modeling behavior that can range from software implementations of algorithms to collections of a large number of register transfer level models.

The implementation of the synthesis tools varies depending on the input language,

and the abstractions of computation and communication in use. While an exhaustive compilation of all proposed and existing high level design methodologies is beyond the scope of this work, most approaches, specially at abstraction levels higher than register transfer level share some common features.

In the remainder of this chapter, we examine the 3 different approaches to the design of a high level methodology. We discuss the fundamental differences between software programming approaches and hardware description languages in terms of their implicit assumptions. We also survey some existing techniques that allow for the limited synthesis of a software description into a RTL level structural hardware description. We examine the utility and drawbacks of nondeterminism in the context of high level description of synthesizable systems. We examine contemporary approaches to high level modeling based on C/C++ programming languages. Then we introduce the concept of rendezvous, a mechanism that performs communication and synchronization as one atomic action. We also examine existing rendezvous based hardware design approaches, in terms of the rendezvous features and modeling flexibility they allow.

### 2.2 High Level Synthesis Methodologies

There have been three basic approaches to the creation of high level design methodologies that are popular in industry today. Most of these have evolved from prior attempts to raise the level of abstraction past RTL for behavioral descriptions. While a thorough treatment of this subject can be found in [Gupta and Brewer, 2008] [Martin and Smith, 2009], they have been broadly classified into 3 categories seen in Table ??

- 1. Software program based

- 2. Extension of RTL design

#### 3. New methodologies

The first approach is to reuse the software based approach to model hardware. In other words, software programs are used to simulate the behavior of digital hardware. In some cases, these simulations can be synthesized into digital hardware as long as the underlying software model is restricted to a small subset of possible features. As hardware systems and software programs exhibit very different properties, arising from fundamental differences, the restriction of software features like threads, or dynamically allocated memory, which have no hardware analogues, is an essential part of modeling hardware using software. A good example would be a tool like Catapult C by Mentor Graphics [McCloud, 2004]. Catapult C is capable of producing a hardware implementable circuit from a C program, given some constraints on the features of ANSI C [ANSI, 1989] used, such as an absence of pointers, the lack of function recursion, and the use of only fixed width primitive data types.

A second popular approach has been to extend existing hardware design methodologies to a higher level of abstraction. A good example of this is Verilog[IEEE, 2001], a standard for RTL design, which was extended to SystemVerilog [Accellera Ltd, 2004] that brought to it features of high level methodologies. The primary advantage of this approach is that since the underlying model is meant to describe hardware, a subset of the higher level methodology remains provably synthesizeable. Additionally, if the syntax remains compatible, then the design work needed for the integration of existing designs into a new high level system description is reduced. The main pitfall of this approach is that the underlying model has severe restrictions due to its roots in hardware design. In SystemVerilog, [Accellera Ltd, 2004] this resulted in the partition of the methodology into a synthesizeable subset and a non-synthesizeable one. This reintroduces the problem of having to maintain separate behavioral and synthesizeable models. The third approach is the design of a new methodology while using familiar language syntax. Typically, this means that the new methodology has an underlying set of assumptions that can model hardware, but the language that the approach uses is similar to, or shares elements in common with, software development languages. A simple example is HandelC [Celoxica Ltd, 2003], an approach that presents a language similar to C, but the underlying methodology communicates via hardware friendly primitives. The primary advantage of such approaches is that the lack of legacy restrictions on behavior allows such methodologies to describe behaviorally systems that have valid hardware descriptions. However, such approaches typically lack a formalism of the underlying communication model [Celoxica Ltd, 2003].

In the case of software approaches that are used to serve as high level hardware models[McCloud, 2004] [Cadence Inc, 2008] [Wakabayashi, 1999], the differences in the implicit assumptions between software and hardware design methodologies become roadblocks. Software approaches inherently assume sequential execution, where one line is executed after the next. Concurrency in software programs, in the form of threads or processes, must be explicitly managed by the programmer. However, this concurrency is not completely controlled by the designer and depends on the operating system's scheduler and provided threading libraries. In contrast, hardware modeling methodologies assume concurrency, or provide a clear mechanism for it within the methodology. Software programs typically make heavy use of dynamically allocated data, and language features such as pointers and recursion which lack hardware analogues. Most importantly, software methodologies have communication methodologies that lack a description in the language but depend on OS semantics. To communicate between two software threads, the operating system plays a significant role. As a result, high level design methodologies that try to synthesize digital hardware systems from existing software programs, rely on the restriction of the input language. The resulting language subset can be used to satisfy an internal hardware centric model and can be synthesized into hardware.

While there are many competing approaches that approach the problem in different ways, one of the main problems that any HLS approach must face is that of lack of formalism[Gajski et al., 1992]. Most high level approaches lack a formal underpinning, which in turn causes the lack of a clear direction for algorithms that convert the description into hardware. As a result, ad hoc mechanisms are employed to model important constructs that occur in hardware. Formal model developed after the methodology only express a subset of the features available[Man, 2005b] [Man, 2005a], making them less useful to designers.

In the next section, we identify the desireable features in a high level design methodology, and categorize them into properties inherent in the methodology and those that arise from the choice of the input description.

### 2.3 Properties for High Level Synthesis

While HLS methodologies are widely varied in their goals and implementations, there are some basic factors that we can say are necessary for any high level hardware design methodology. These are based upon criteria discussed in [Gajski et al., 1992] for the general methodology criteria and from [Edwards, 2005b] and [De Micheli, 1999] for the language criteria.

The properties can be divided into properties based on the methodology itself, and those that are dependent upon the language that is used for the methodology. This is an important distinction, but one that is sometimes useless in practice. In many cases, the methodology and the language that supports it are so closely tied together that the properties become interchangeable. This distinction, however, allows us to compare some very differing approaches to see their properties.

| Methodology                 | Language Specific |  |

|-----------------------------|-------------------|--|

| Formal Theory               | Concurrency       |  |

| Flexible Modeling Semantics | Communication     |  |

| Abstraction Levels          | Data Type Support |  |

| Nondeterminism              |                   |  |

Table 2.1: High level design criteria

A good high level synthesis methodology should firstly posses some formal underpinning for the system so that models can be converted into hardware. In the case of many methodologies, especially those that try to use a software paradigm to model hardware, such as ANSI C [ANSI, 1989], it is their ad hoc nature that prevents their synthesis to hardware. The lack of a coherent formal model for high level methodologies means that there is no consistent methodology for the creation of hardware circuits. Furthermore, the formal model is essential to perform design verification and model checking. In modern systems, verifying the functionality of the system is an increasingly important part of their design. The use of formal verification tools allows for the design of larger systems. In many approaches for high level modeling, the final formal model incorporate a multitude of differing incompatible formal models, it becomes impossible to reconcile all the formalisms to create a provably correct design [Edwards et al., 2001]. This problem has been addressed previously in [Gajski et al., 1992] and [Camposano and Wolf, 1991].

The primitives that are proposed by the methodology must lend themselves to usage in a wide variety of modeling scenarios. As systems can be modeled in different ways, and different types of systems possess widely varying characteristics, it is important that the basics of the methodology can be adapted for use in all these cases. In the absence of such flexibility, the methodology designer is forced to create a new primitive for each new scenario. This results in the creation of niche modeling methodologies that are capable of describing particular systems, but are not general. As high level models lack of a unifying formal model, this means that large designs that may require multiple different models will not be synthesizeable.

High level approaches generally possess the ability to model multiple abstraction levels, or at least use some design basis that supports design refinement[Gajski et al., 1992]. Refinement is the term used to describe the conversion of a more abstract model into a more concrete one, usually by the addition of constraints such as timing information, area or power guidelines. This is an important step for any design methodology, and any new high level methodology should be able to perform some level of refinement. Since high level tools maintain support for a wide variety of abstraction levels, their formal models are a mixture of behavioral, finite state machine, and register transfer formalisms, with no model for the entire approach. As a result, it becomes impossible to synthesize the full set of possible designs and features that the approach supports. Another important factor is that while high level approaches present abstractions for computation that can be easily refined, their abstraction for communication cannot always be. Further, the lack of a standard way to abstract communication means that different designers abstract communications in incompatible ways even while using the same high level approach.

Nondeterminism is a property of high level models that allows the designer to succintly express complex behaviors, by leaving unknown or undesired behavior unspecified [Armoni and Ben-Ari, 2009]. This reduces the size of the behavior that the designer must specify, reducing design time. However, nondeterminism is an undesireable property in a synthesized description. As a result, a good high level design methodology is capable of accepting nondeterminism in its input specification, but has a formal way to convert this specification into a deterministic one. This allows the designer to flexibly express the system while seeing predictable results. The role of nondeterminism is addressed in depth in Section 2.5.

Another set of considerations come about from the language used to implement the methodology. The primary cause for these issues is the disconnect between software programming languages and hardware design languages.

## 2.4 Differences between Hardware Description Languages (HDLs) and software programming languages

As high level hardware descriptions can be sometimes expressed as algorithms and due to the larger number of designers familiar with software programing, many approaches try to make high level design as close to software design as possible [Sangiovanni-Vincentelli, 2003]. The basic differences between hardware design and software programming, many of which are implicit in the assumptions made prevent the easy use of a single approach that is capable of being both a software programming and a hardware description language.

The most important of the differences between software programming and hardware description languages, is the matter of concurrency and its description. In software programming languages, the code is assumed to be executed sequentially. Concurrency is explicitly implemented, either using threads [Liao et al., 1997] or by using keywords such as "par" in BachC [Kambe et al., 2001]. Hardware design languages, on the other hand, usually have concurrency defined as an implicit part of the language, such as in Verilog [IEEE, 2001] and VHDL [IEEE, 2000]. In addition, they support the notion of a "nonblocking" or parallel assignment. This fundamental difference in the definition of concurrency affects the design of the approach immensely.

Many high level approaches rely on the use of the hardware centric definition of concurrency, where each module or structural unit is assumed to be performing computations and communications in parallel[Gajski and Ramachandran, 1994]. Approaches that extend existing hardware design semantics, or that have created their own language are able to work around this easily. However, approaches that attempt to extend software programming to high level modeling and synthesis are forced to define new semantics. In the case of languages like SystemC [Automation, Design and Committee, Standards, 2006], each concurrent action is explicitly created and registered with the simulation engine. Thus, while the global notion of implicit concurrency is not present, the language semantics allow the explicit declaration of concurrent blocks of sequential code.

Communication as a language property that can be examined in all three contexts differently. In the case of hardware design languages, communication usually happens over fixed channels, but can support reactive inputs, through constructs like wires. In general, communication for RTL and lower HDLs is over wires that can be bidirectional and are of fixed size. Wires model hardware systems well and allow for bidirectional communication, synchronous communication and multiparty communication. In software programming languages, the fundamental method of communication is a function call, a unidirectional, asymmetric code reuse mechanism. Function calls can be used to model more complex communications by making the new modules for communication primitives. Function calls do have some advantages over the use of wires - their support for different data types and the flexibility of their composition. However, they have limited support for bidirectional communication, cannot handle multiparty communication well, and cannot model reactive inputs. New methodologies usually introduce their own communication primitives. Most methodologies allow for multiple communication primitives, to model different kinds of communication patterns.

The basic representation of data is another intrinsic property of the language

that affects the final approach. In the case of hardware design languages, data types are usually of fixed size, and do not support pointers. In software programming languages, data types can have variable sizes, or can be implemented as pointers. Most new approaches usually assume data types to be fixed in most cases, but allow for some flexibility to be able to model software patterns as well.

### 2.5 Nondeterminism

Nondeterminism in an important property in any high level synthesis approach. Nondeterminism refers to the case where given an input and a current state for a system, there are multiple possible next states. To put it in terms of the approach, nondeterminism is the property that arises from the ability to incompletely specify behavior of the model. This flexibility is crucial for high level approaches as it helps keep the input size small, while maximizing the behavior of the system. The presence of nondeterminism allows the modeling of complex practical designs in a simple fashion.

The concept of nondeterminism was first proposed in [Rabin and Scott, 1959]. In it, nondeterminism was proposed in the context of finite automata. A few years later, [Hopcroft et al., 1979] further formalized the concept of nondeterministic finite automata (NFAs). The equivalence of NFA and their deterministic counterparts was established, thus allowing the properties of deterministic finite automata to be applied to NFAs. In [Carrol and Long, 1989], a way to implement circuits from NFA descriptions is covered. As there was an equivalence between DFA and NFA, there is a way to reduce nondeterminism in a system. A clear formal proof of the power of nondeterminism to reduce the complexity of input descriptions is given in [Drusinsky and Harel, 1994]. Effectively, the presence of concurrency and nondeterminism in an input description exponentially reduces its size.

Nondeterminism is a practical mechanism for avoiding the complete description

of a system. In doing so, nondeterminism helps raise the level of abstraction. This was first pointed out in [Dijkstra, 1975]. By delaying the specification of implementation details, the presence of nondeterminism allows the designer to create the overall system behavior instead of the details of each stage.

A complete survey of nondeterminism is presented in [Armoni and Ben-Ari, 2009]. In it, the classification of nondeterminism based on 6 major properties is proposed and studied. [Armoni and Ben-Ari, 2009] also presents a distinction between nondeterminism arising from concurrency and nondeterminism arising from the property of an automata. A hardware implementation of a sequential process cannot contain nondeterminism as, at any given instant, the hardware will be in a fixed state. In order to ensure the creation of deterministic hardware that can be debugged, it becomes important that there exist a construction that can convert the nondeterministic system into a deterministic one in a fixed fashion. While the construction of NFA from a DFA is discussed in [Carrol and Long, 1989], the resulting deterministic automaton is exponentially larger.

The basic use of nondeterminism in high level approaches is clear. Nondeterminism is a powerful mechanism to reduce the complexity of designs, while allowing the designer to refrain from expressing unnecessary amounts of detail. This mechanism allows for the easy increase of the level of abstraction, an essential part of high level design. Formally, we can show that nondeterminism provides for exponential reductions in input design complexity, while still retaining a path to synthesis.

### 2.6 C/C++ Based approaches

In general, high level synthesis approaches can be divided into three major categories - approaches based on using and extending existing software design methodologies, those based on extending hardware design methods and those based on new methodologies that use a familiar syntax. A popular starting language is C. The proponents of this approach claim that familiarity with the language and that the benefit of being able to co-design both the hardware and the software of a system give it a significant advantage [Edwards, 2005a]. C, a language originally developed by Kernighan and Ritchie [Kernighan and Ritchie, 1988] was intended as a low level language, with a very tight correspondence to the assembly language. The resulting approach provided syntactic structures that simplified design tasks, but retained a correspondence to the microprocessor architecture. However, some of the choices made resulted in problems when it came to synthesizing general hardware from a C description. The introduction of data types that were not inherently fixed to hardware representations, and the introduction of pointers meant that a generic C program could not be guaranteed to create hardware. As a simple example, if we consider an array, a basic hardware type, is represented in C as a pointer, it becomes clear that unless the synthesis tool performs analysis of the pointer and its usage, it cannot determine how to size the resulting array. Thus, all C based approaches only accept a subset of C for synthesis. Some popular C based approaches include Cones [Stroud et al., 1988], HardwareC [Ku and De Micheli, 1990], SpecC [Gajski et al., 2000b] [Fujita and Nakamura, 2001] and BachC [Kambe et al., 2001].

Cones, introduced in 1988, was a very early approach to high level synthesis from C. By considering a very limited subset of C, and disallowing features like unbounded loops or pointers, cones could create gate level hardware from a C description. HardwareC was a new hardware modeling methodology that aimed to extend C like semantics to hardware. Despite its similarity and the naming, HardwareC is fundamentally different from C in that the basic language does not support pointers, assumes a global clock, and expresses concurrency through the use of modules. Thus, there is no advantage of designer familiarity with C. Additionally, general communication

| Hardware Based | Software Based   | New Methodology |  |

|----------------|------------------|-----------------|--|

| Verilog        | Cones            | SpecC           |  |

| VHDL           | Cyber            | HardwareC       |  |

| SystemVerilog  | C2Verilog        | BachC           |  |

|                | Transmogrifier C |                 |  |

|                | CatapultC        |                 |  |

|                | C-to-silicon     |                 |  |

Table 2.2: Approaches to HLS

patterns are difficult to express in HardwareC. For example, modeling the arbitration of resources cannot be done abstractly, as HardwareC has no support for it. SpecC is fundamentally a specification language, subsets of which are synthesizable. Like HardwareC, SpecC is a new methodology whose syntax looks very similar to ANSI C. By introducing a few more keywords for parallel composition of statements, and by introducing separate channels for communication SpecC attempts to simplify hardware design. However, the lack of a clear definition for atomicity, and the absence of a way to define mutual exclusion presents some shortcomings. BachC was an attempt to bring the communication semantics of Occam [Barret, 1992] to C. As a result, BachC faces a similar set of challenges as Occam, and is explained further in depth in the next section.

Another direction that was considered was the use of more complex synthesis tools with C. The modifications made to the C design itself were very minor, i.e. either used a restricted subset of the input language or provided some bounds on software constructions such as pointers. Cyber, an approach introduced by NEC [Wakabayashi, 1999] [Wakabayashi, 2004], used a variant of C that prohibited recursion and pointers. C2Verilog was a synthesis tool that accepted almost a complete set of ANSI C to create a Verilog circuit [Soderman and Panchul, 1998]. Transmogrifier C [Galloway et al., 1995] was a synthesis tool that used a small subset of C to generate hardware descriptions that could be easily used on an FPGA. The scenic design environment [Liao et al., 1997] was an approach that simplified the expression of concurrency by modeling each module as a parallel lightweight thread. Cosyma [Ernst et al., 1996], took a different stance and used the C based description to create a partition of the hardware and software environments. It would synthesize the subset of C it could, and allow the remainder to be executed as software. Additionally, attempts such as SpC [Semeria and De Micheli, 1998] tried to show that in many cases, pointers could be resolved fully at synthesis time, and therefore allow a commonly used C language construct in the synthesizable subset.

The newest of the C/C++ based HLS methodologies are CatapultC by Mentor [McCloud, 2004] and C-to-Silicon by Cadence [Cadence Inc, 2008]. Both of these are capable of using a very large subset of C and can create gate level netlists from the C model.

Finally, the most popular high level modeling methodology is based on SystemC [Automation, Design and Committee, Standards, 2006]. SystemC has wide support in the EDA industry for the specification of models at a high level. Communication in SystemC is handled by abstract channels. These channels are C++ classes implemented using wait() and notify() function calls. While the description is flexible from a software programming point of view, it is not possible to synthesize an arbitrary channel as it lacks a hardware equivalent. Further, the channels follow delayed update semantics, and behave more like registers in RTL HDLs like Verilog, rather than as wires or combinational paths. The lack of wires makes the expression of reactive systems in SystemC slightly cumbersome. Concurrency in SystemC is handled explicitly, where each module is declared as an independent sc\_thread or sc\_method.

SystemC sc\_threads closely resemble software threads, implementing a form of cooperative multithreading and share many of the same properties. As a result, HLS tools like C-to-silicon and CatapultC cannot synthesize modules containing threads. SystemC methods are typically used to implement combinational elements. While clocks can be declared manually, the notion of clocking is implicit in SystemC, the execution of these models happens using a delta time update approach. Combined with the delayed update semantics of the communication channels, every communicating module in SystemC effectively behaves as a register transfer stage, containing the combinational update logic and the buffered data output. While SystemC supports the intrinsic C++ data types, synthesis tools usually prefer the use of SystemC specific types. These types support fixed width integers, fixed and floating point numbers and strings. Again, not all of these are synthesizable and depend heavily on the synthesis tool.

The style of modeling most used with SystemC to create the high level approach is referred to as Transaction Level Modeling (TLM) [Cai and Gajski, 2003]. While TLM is supposed to be a generic high level design approach, the reference implementation is in SystemC[Maillet-Contoz and Ghenassia, 2005]. As a result, features of SystemC came about due to the TLM semantics, and vice versa. The primary goal of TLM is to further subdivide the levels of abstraction and provide a path from an abstract, untimed, specification to a timed, cycle accurate computation based model. Some example TLM flows are presented in [Donlin, 2004], and show the heavy reliance of TLM models on the communicating process abstraction level of TLM. However, there are no formal models, or well defined synthesis flows for TLM. Additionally, portions of the specification are implemented using event function calls that modify the scheduler's event queue, making it difficult to synthesize directly. Finally, the TLM approach relies very heavily on the user, who needs to guide each step in the refinement. As a result, the designer must be familiar, not only with software programming, but also, low level hardware design.

While the SystemC methodology itself lacks formal semantics and is ad hoc, there has been work on a subset of SystemC that can be described formally [Man, 2005b] [Man, 2005a]. Further, the basic form of communication, channels, are not close analogues of hardware wires. More importantly, SystemC is able to provide dataflow semantics, but the control flow semantics and synchronization are not handled in a scalable hardware friendly way. Finally, SystemC is not generally synthesizable, and leads to the requirement of maintaining a RTL implementation that can actually be implemented and a SystemC implementation that is used to verify the specification, leading to duplication of work and the potential for errors.

### 2.7 Introduction to Rendezvous

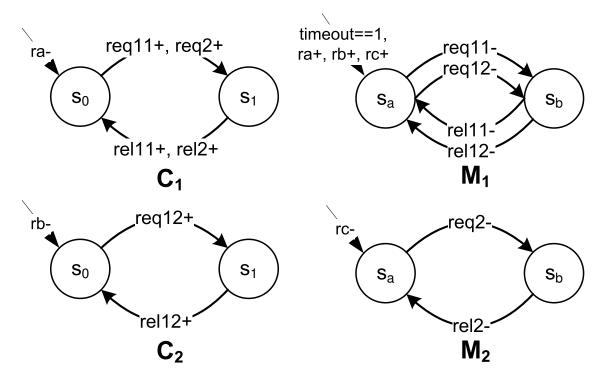

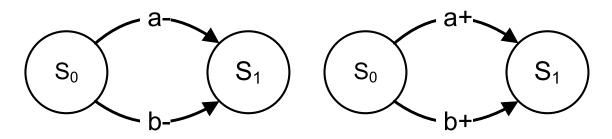

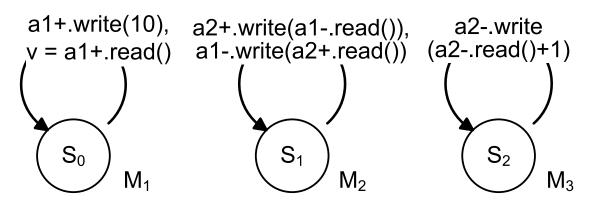

The concept of rendezvous was first introduced in CSP [Hoare, 1978] and CCS [Evangelist et al., 1989]. A rendezvous is generally regarded as an atomic, synchronous communication mechanism among processes. In its simplest bi-party form, two processes wait for each other at their respective rendezvous points where they expect to communicate. When both parties reached the rendezvous points, the rendezvous occurs, allowing both processes to continue to progress. In its more general form, as pointed out by [Joung and Smolka, 1996], we can define a rendezvous as an n party interaction with k roles. A role is a particular type of participant for the interaction and could be satisfied by a fixed or a variable set of parties.

We can then further classify rendezvous based on which primitive composition rules are allowed. *Conjunction* is the case where multiple rendezvous must occur simultaneously. *Disjunction* is the case where only one of a set of rendezvous occurs at a given time. A system can then be classified based on the allowed freedom of composition of these basic rules. In summary, the use of rendezvous can be classified based on the following characteristics.

- 1. Multipartiness the number of parties involved in each occurrence of a rendezvous

- Variability whether participants for each party of a rendezvous must be a fixed set of processes or a variable set

- 3. Composition Rules the number of restrictions placed on the combination of the primitives below.

- (a) Disjunction whether a rendezvous can be used in disjunction so that one of several choices should occur

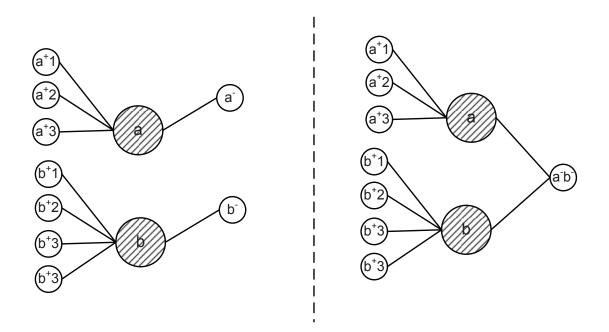

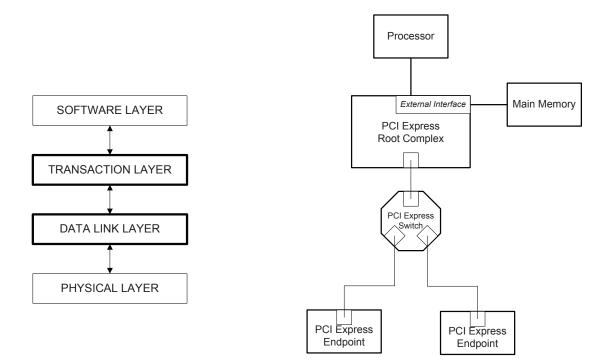

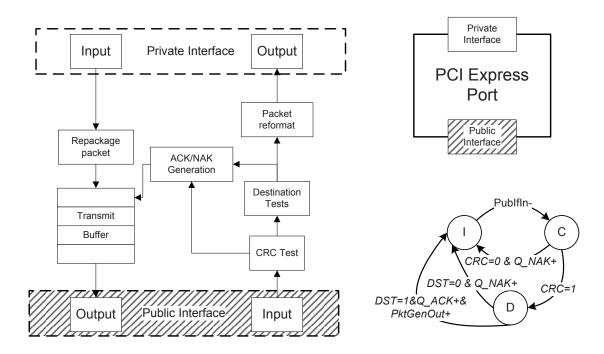

- (b) Conjunction whether a rendezvous can be used in conjunction so that several rendezvous must jointly occur